微型计算机原理与系统设计

第一章 绪论:微型计算机概述

第一讲 微型计算机概述

基本概念

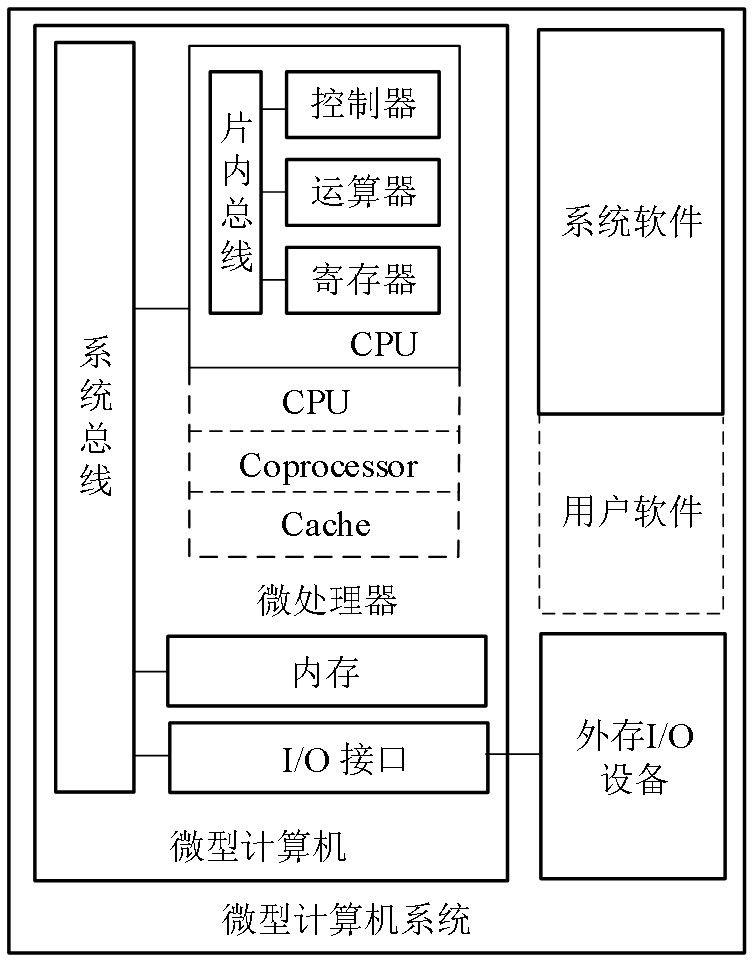

| 微型计算机系统的三个层次:微处理器、微型计算机、微型计算机系统 |

|---|

微型计算机系统层次结构

- 微处理器:由 1 片或几片大规模集成电路组成的中央处理器,也即微型计算机中的 CPU (中央处理单元),具体包括控制器、运算器、寄存器以及连接三者的片内总线;

- 微型计算机:微处理器、内存、I/O 接口以及连接三者的系统总线或芯片组的集合,也即裸机;

- 微型计算机系统:以微型计算机为中心,配以相应的外围设备以及控制微型计算机工作的软件,简称为微机;

- 软件:系统软件和应用软件;

- 外设:外存和 I/O 设备;

- 单片机:CPU、内存、I/O接口以及使三者互连的总线在一个芯片上的集成,也即微型计算机在一个芯片上的集成;

- 单片机系统:由单片机、专用软件和 I/O设备组成的系统,常用于特定任务的控制或处理;

| 单片机系统具有专用性,微型计算机系统具有通用性 |

|---|

微处理器概述

- Intel微处理器发展

| 时间 | 型号 | 位宽 | 主频 | 制造工艺 |

|---|---|---|---|---|

| 1971年 | 4004 | 4位 | 108KHz | 10μ |

| 1972年 | 8008 | 8位 | 500-800KHz | 10μ |

| 1974年 | 8080 | 8位 | 2MHz | 6μ |

| 1978年 | 8086 | 16位 | 5MHz | 3μ |

| 1979年 | 8088 | 16位 | 5MHz | 3μ |

| 1982年 | 80286 | 16位 | 6MHz | 1.5μ |

| 1985年 | 80386 | 32位 | 16MHz | 1.5μ |

| 1989年 | 80486 | 32位 | 25MHz | 1μ |

| 1993年 | Pentium I | 32位 | 66MHz | 0.8μ |

| 2001年 | Itanium | 64位 | 66MHz | 0.8μ |

第二章 Intel 单核/多核处理器

第一讲 单核处理器(Intel 8086处理器)

8086/8088 处理器功能特性

- 16 位微处理器(内部数据总线)

- 引进指令级流水

- 引入分段管理机制,扩大寻址空间

- 只有整数运算能力,配套数值协处理器 8087、输入/输出协处理器 8089,具备较强大计算能力和 I/O处理能力

- 8086:16位;8088:8位(外部数据总线)

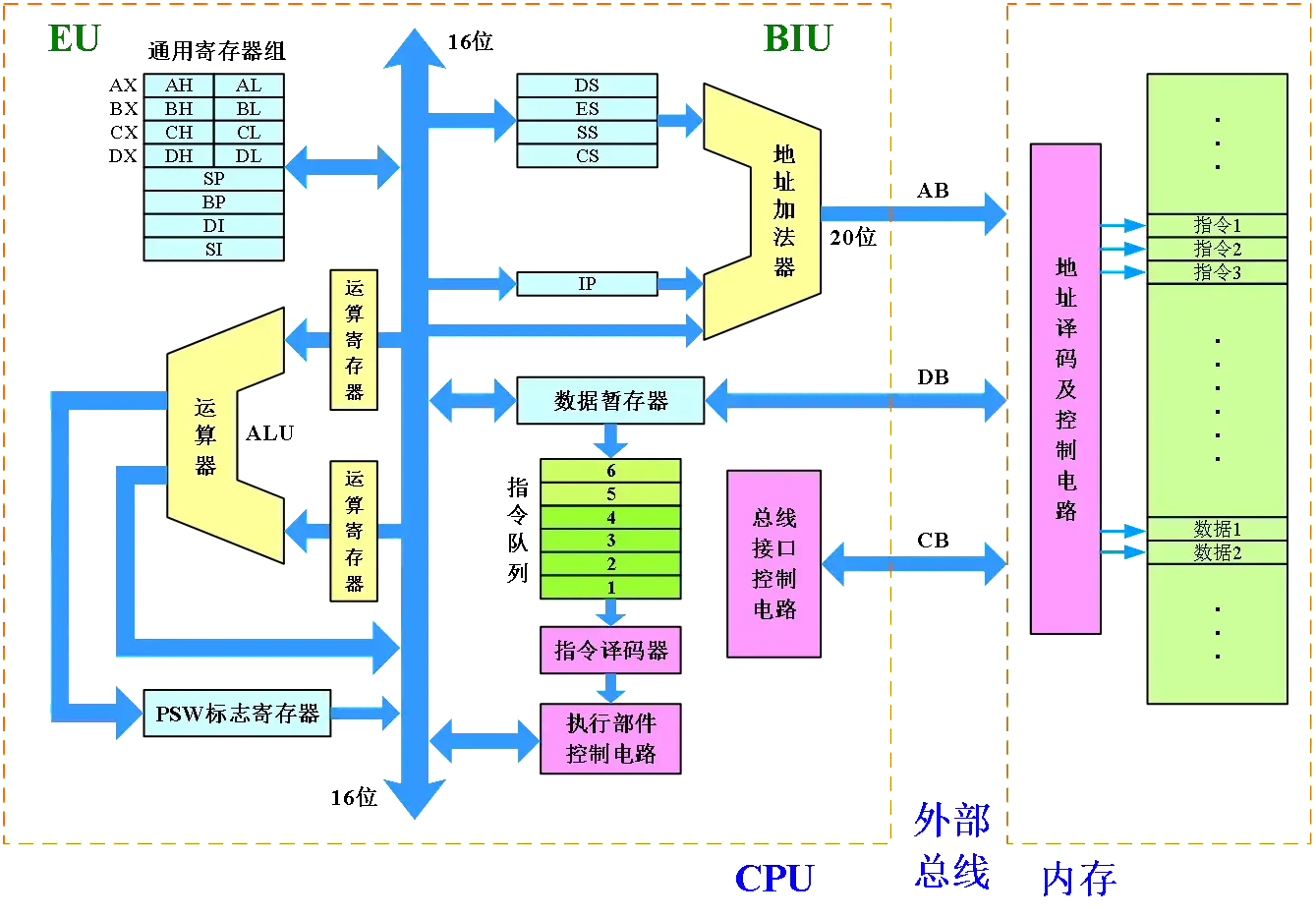

8086处理器的体系架构

8086处理器体系架构

【组成部分】

8086处理器分为两个部分:执行单元 (Execution Unit, EU) 和总线接口单元 (Bus Interface Unit, BIU)

- 执行单元

- EU负责指令的执行,包括ALU(运算器)、通用寄存器组和状态寄存器

- 执行的运算:算术、逻辑、移位运算及段内偏移地址(即有效地址)的计算

- 总线接口单元

- BIU负责与主存和I/O设备的接口,由段寄存器、指令指针、地址加法器和指令队列缓冲器等组成

- 主要操作:取指令、与主存或I/O设备交换数据

【工作机理】

EU与BIU并行工作

BIU在指令队列缓冲器有2个以上字节时就不断从主存连续地址单元中取得指令送入指令队列缓冲器中,EU则不断从指令队列缓冲器中取出指令加以译码执行

异常情况:

- 当6个字节的指令队列缓冲器满,且EU没有主存或I/O访问请求时,BIU进入空闲状态;

- 当EU执行访存或I/O指令时,BIU在执行完当前周期后,暂停取指令操作,在下一总线周期执行EU所要求的主存或I/O读写操作,之后再继续BIU的取指操作

- 当EU执行转移、调用、返回等程序跳转类指令时,BIU会清除之前读入指令队列缓冲器的无效指令,并根据EU提供的跳转指令,重新获取跳转后的程序段指令

【创新特点】

8086处理器引入指令队列缓冲器使得预取指令变为现实,取指令和执行指令可以并行执行,从而加速了程序的运行.

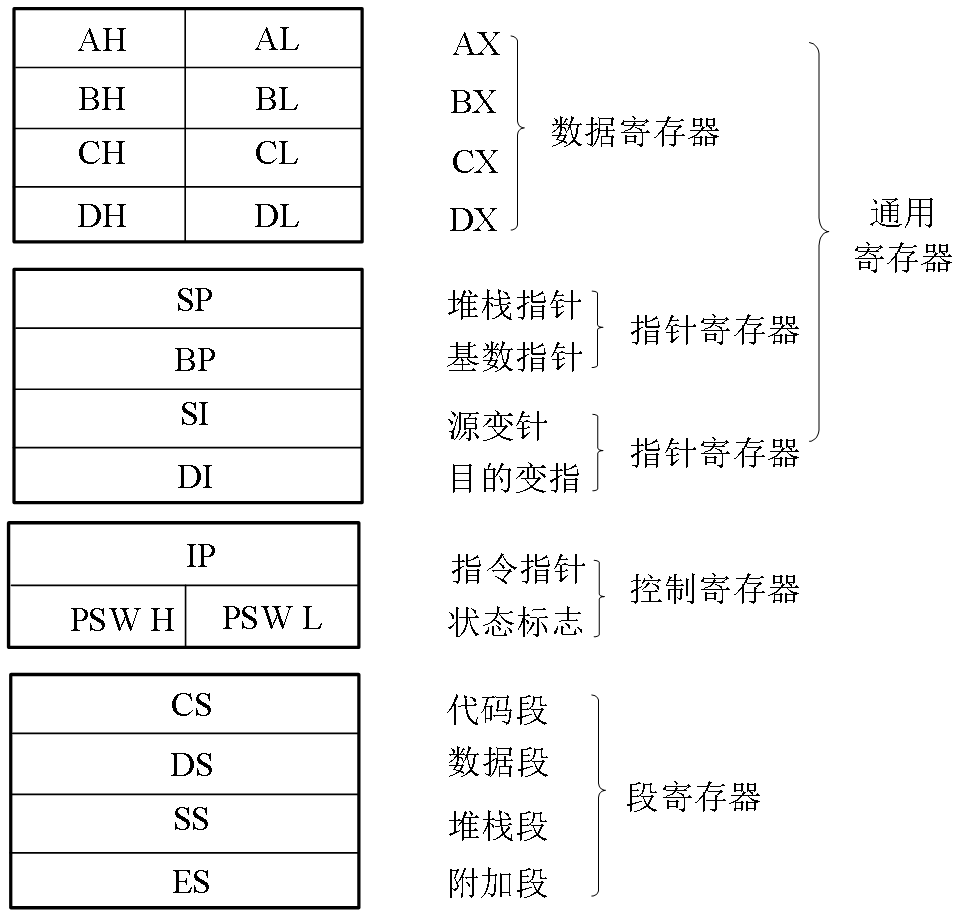

8086处理器的寄存器

8086处理器有14个寄存器:8个通用寄存器(4个数据寄存器、2个指针寄存器和2个变址寄存器)、2个控制寄存器和4个段寄存器.

8086处理器的寄存器配置

【数据寄存器】

- 16位数据寄存器:AX、BX、CX和DX,可以存放16位的源操作数或目的操作数

- 为了支持字节操作,每个寄存器又分为两个8位的高、低字节寄存器:AH、AL、BH、BL、CH、CL、DH、DL

【指针寄存器】

- SP(Stack Pointer)堆栈指针寄存器用于存放主存中堆栈区的偏移地址,指示堆栈的当前操作位置

- BP(Base Pointer)基数指针寄存器用于存放主存的基本偏移地址

【变址寄存器】

- SI(Source Index)源变址寄存器,指向源操作数,具有自动修改内容的功能

- DI(Destination Index)目的变址寄存器,指向目的操作数,具有自动修改内容的功能

【控制寄存器】

- IP(Instruction Pointer)指令指针寄存器,指示当前指令所在存储单元的段内偏移地址;当8086 CPU根据CS和IP取得一个指令字节后,IP便自动加1(顺序执行),指向下一条待读取指令

分析

8086处理器采用分段存储管理机制,CS段寄存器存放当前指令所在内存段的首地址,IP存放当前指令所在内存段内偏移地址,以此来获取指令的地址;操作系统执行程序时,将首地址加载至CS和IP中,转移类指令执行时:如果目标地址与程序首地址所在同一段,就用目标地址修改IP;如果目标地址与程序首地址在不同段,就用目标地址同时修改CS和IP.

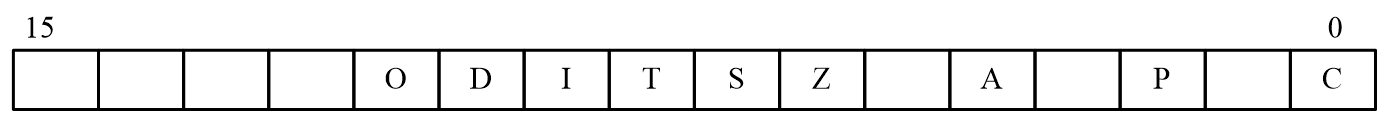

- PSW(Program Status Word)程序状态字,也称程序寄存器或标志寄存器,存放CPU工作过程中的状态信息

程序状态字

【标志位】——16位暂定义了9个标志位

- C——进位标志位,加减运算时标识最高位出现进位或借位,受逻辑运算、位移和循环指令的影响

- P——奇偶标志位,标识运算结果低8位中1的个数是否为偶数

- A——半加进位标志位,加减运算时标识低4位向高4位是否进位或借位,用于对BCD结果的校正

- Z——零标志位,标识运算结果是否为全0

- S——符号标志位,标识运算结果是否为负数,当运算结果最高位为1时,该标志位置为1

- T——单步标志位(陷阱标志位),标志位置为1时,8086处理器进入单步执行指令方式;每条指令执行完毕时,CPU测试T标志位:若T=1则在当前指令执行后产生单步中断(陷阱中断),CPU执行陷阱中断处理程序:该程序能够显示当前指令执行结果,为程序调试提供必要的信息

- I——中断允许标志位,该标志位为1时,CPU可响应可屏蔽中断请求,否则不响应可屏蔽中断请求

- D——方向标志位,若该标志位为1,则SI和DI在串操作指令执行中自动减量,即从高地址到低地址处理字符串,否则在串操作指令执行中自动增量

- O——溢出标志位,标识带符号数运算结果是否超出8位或16位表示范围

【段寄存器】

组成:代码段寄存器 CS(Code Segment)、数据段寄存器 DS(Data Segment)、堆栈段寄存器 SS(Stack Segment)和附加段寄存器 ES(Extra Segment)

作用:存储不同属性段的段地址,与有效的段内偏移地址一起确定主存的物理地址; CS指示程序区,DS和ES指示数据区,SS指示堆栈区

8086 主存储器和 I/O结构

【主存分段存储管理机制】

8086处理器的主存物理地址由段地址和段内偏移地址确定,且主存空间: 1MB,每段大小: 64KB,则可以划分的虚拟段数为:

1MB64KB=220B216B=24

因此 1MB 主存可以划分为24 个不重叠的存储段,对于段起始地址(有效高四位)采用低位对齐策略即段起始地址的低4位全为 0,可以使得 20 位段地址降低为 16 位,调整段起始地址又可以指定不同存储段因此又可以划分为 216 个重叠的存储段;段内偏移地址(有效低16位)可以决定段内的地址.

BIU 中有一个地址加法器,作用是将 16 位段地址左移 4 位,然后与 16 位段内偏移地址相加,生成 20 位的物理地址:

Memory Address=CS×16+IP

每个存储单元的地址标识:20 位物理地址/逻辑地址(段地址 16 位:段内偏移地址 16 位)

由上式可以看出,8086处理器可以提供20位的地址,对主存单元寻址使用全部20位地址,对I/O设备端口寻址使用其低16位地址:1M的主存存储空间、64K的I/O设备端口空间

【主存结构设计】

- 支持字节操作:8086处理器采用字节编址方式,即主存或I/O的一个地址单元内存储一个字节,实现根据地址进行1字节的存储器或I/O设备的读/写操作

- 支持16位数据操作:字节编址方式下使用两个连续地址来访问16位数据,并按小段模式存储,实现16位存储器或I/O操作

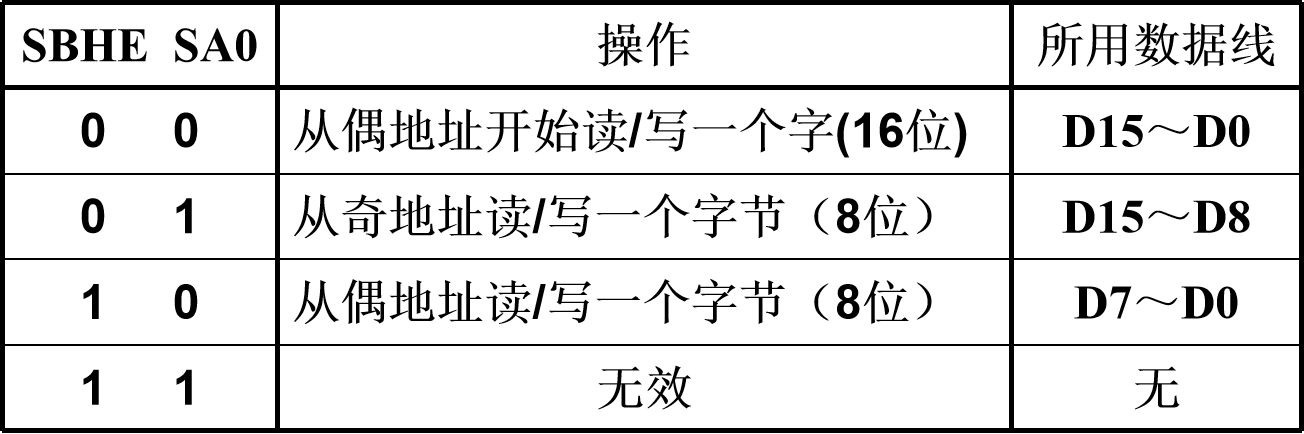

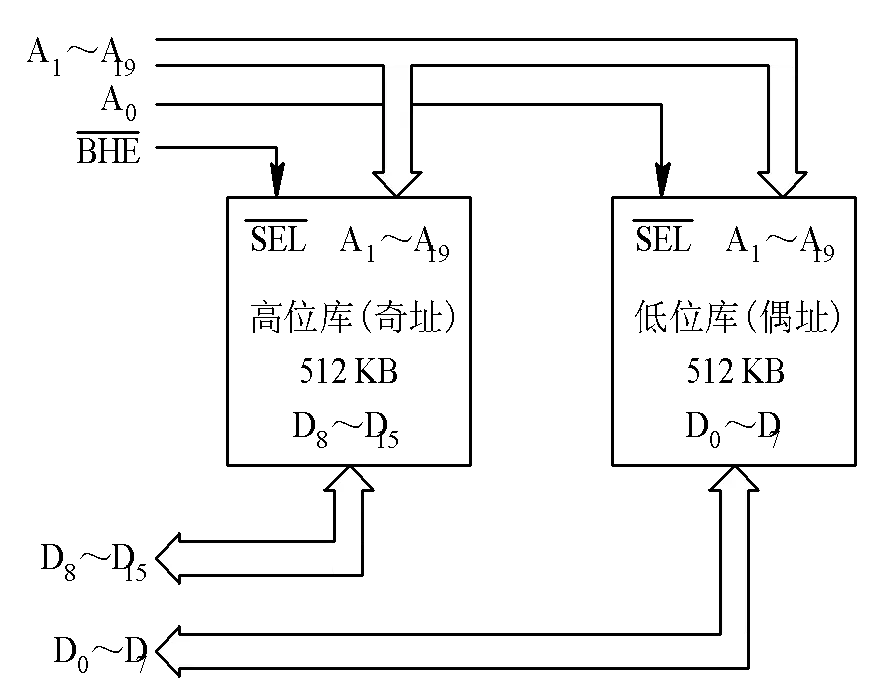

【主存和I/O系统的分体结构】

主存的存储空间和I/O的端口空间均采用奇、偶双体存储器,偶地址对应低字节的访问,通过低字节允许信号 A0=0 选择;奇地址空间对应高字节的访问,通过高字节允许信号 ¯BHE=0 选择;

| ¯BHE | A0 | 操作说明 |

|---|---|---|

| 0 | 0 | 高字节体与低字节体同时有效,给定地址n∗,从主存或 I/O 空间读写16位数据 |

| 0 | 1 | 高字节体有效,给定奇地址n,从主存或 I/O 空间读写8位数据 |

| 1 | 0 | 低字节体有效,给定偶地址n,从主存或 I/O 空间读写8位数据 |

| 1 | 1 | 高字节体和低字节体无效,不能访问主存或 I/O 空间 |

注 ∗:

当 n 为偶地址时,仅需一个总线周期就可以完成 2 字节的读/写,其中 地址 n 读/写数据低 8 位,地址 n+1 读/写数据高 8 位(主存按字节编址);当 n 为奇地址时,则需要两个总线周期才可以完成 2 字节的读/写,其中第一个总线周期从地址 n 读/写数据低 8 位,第二个总线周期从地址 n+1 读/写数据高 8 位(主存按字节编址);

(总线周期:CPU通过系统总线对主存或 I/O 设备进行一次读/写访问所需的时间)

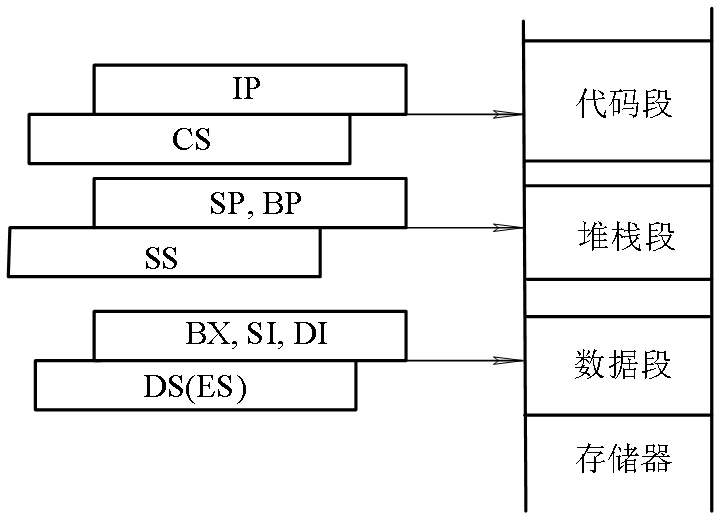

【数据按属性分段存储】

8086处理器设置了 4 个属性的存储段:程序段(代码段)、数据段、堆栈段和附加段,并用段寄存器 CS、DS、SS 和 ES 分别为 4 个属性段提供段地址. 在访存操作中,段地址由“默认”或“指定”的段寄存器提供:

- 段寄存器的默认使用情况

段寄存器的默认使用情况

段寄存器的指定使用情况

通过在指令中增加一个字节的段超越前缀指令来实现:MOV AL,ES:[BX](从存储单元 (ES:BX) 中读取数据)

8086处理器芯片引脚

| 关注方面 | 作用 |

|---|---|

| 引脚功能 | 引脚信号的定义、作用 |

| 信号的流向 | 输出、输入、双向 |

| 有效电平 | 高电平有效、低电平有效、上升沿有效、下降沿有效 |

| 三态能力 | 低电平、高电平、高阻 |

【8086 CPU 引脚分析——工作条件】

| 名称 | 方向 | 有效电平 | 功能 |

|---|---|---|---|

| VCC | Input | +5V | 工作电源 |

| GND | Input | 1 | 接地端 |

| CLK | Input | 5MHz | 时钟信号 |

| RESET | Input | 1 | 复位信号 |

| MN | Input | 1 | 最小工作模式 |

| MX | Input | 0 | 最大工作模式 |

| AD0∼AD15 | Input/Output | 三态 | 地址或数据总线 |

| A16∼A19 | Output | 三态 | 地址总线 |

| BHE | Output | 三态 | 高字节允许信号 |

| INTR | Input | 1 | 可屏蔽中断信号 |

| INTA | Output | 三态 | 对INTR 请求信号的响应信号 |

| READY | Input | 1 | 准备就绪信号 |

| TEST | Input | 0 | 测试信号 |

| DT/¯R | Output | 三态 | 数据发送/接受控制信号 |

| DEN | Output | 三态 | 数据有效信号 |

| ALE | Output | 1 | 地址锁存信号 |

I. 两种工作模式下的共用信号

【A16∼A19/S3∼S6】

A16∼A19 与 S3∼S6 分时复用信号,S6 始终为0,S5 表示中断允许标志的状态,S4、S3 指示 CPU 正在使用的寄存器;

【¯BHE/S7】

分时复用信号,¯BHE 在总线周期的 T1 时钟周期起作用;S7 为备用状态;

【RESET】

复位信号,当 RESET 返回低电平时,CPU重新启动;

【READY】

CPU读写主存或 I/O 设备时,在总线周期的 T3 时钟周期采样 READY 信号;当为低电平时,需要在 T3 周期之后插入等待周期 TWAIT ;

【INTR】

CPU 在每条指令执行的最后一个时钟周期采样该信号,以决定是否进入中断响应周期;

【NMI】

非屏蔽中断请求信号,上升沿有效,中断不可被屏蔽,NMI 请求的优先级高于 INTR 请求;

【¯INTA】

在响应中断过程中,由 ¯INTA 送出两个负脉冲,在第二个 INTA 周期 CPU 获得外部中断源的中断向量码;

【DT/¯R】

数据发送/接受控制信号,高电平控制数据发送;低电平控制数据接受;

【¯DEN】

数据有效信号,表示 D0∼D15 的数据是否有效;该信号在最小模式下由 8086 提供,低电平有效,在最大模式下由 8288 提供,高电平有效;

【ALE】

地址锁存信号,高电平有效,表示 A0∼A19 上的地址有效;

II. 最小工作模式

当MN/¯MX=1 时, 8086 CPU工作在最小模式,微机中只有一个处理器,系统总线仅由CPU信号形成;

【M/¯IO(输出、三态)】

低电平访问 I/O 设备;高电平访问主存;

【¯RD(输出、三态)】

低电平有效,表示CPU正在读主存或 I/O 接口;

【¯WR(输出、三态)】

低电平有效,表示CPU正太写主存或 I/O 接口;

【HOLD(输入)】

保持请求信号,高电平有效,表示某总线设备请求使用系统总线;

【HLDA(输出、三态)】

保持允许信号,高电平有效,表示 CPU 对 HOLD 请求的响应信号;

III. 最大工作模式

当MN/¯MX=0 时, 8086 CPU工作在最大模式,微机中除了主处理器8086,还允许接入其他协处理器(运算处理器8087、I/O 处理器8089)构成多微处理器系统,系统总线由 8086 和总线控制器 8288 提供的信号共同形成;

【¯S0、¯S1、¯S2(输出、三态)】

表示该总线周期存取哪种设备的状态信号,是 8288 产生控制信号的依据;

【8288 不同之处】

- 8288 的 DEN 信号为高电平有效;

- 8288 通过 ¯MRDC(存储器读信号),¯MWTC(存储器写信号)、¯IORC(I/O 读信号)、¯IOWC(I/O 写信号)来控制对主存或I/O的访问;

【¯LOCK(输出、三态)】

总线索存信号,低电平有效,信号有效期间,总线请求信号被封锁;

【QS0,QS1(输出)】

表示指令队列缓冲器存取的状态信号:

| QS1 | QS0 | 性能 |

|---|---|---|

| 0 | 0 | 无操作 |

| 0 | 1 | 队列中操作码的第一个字节 |

| 1 | 0 | 队列空 |

| 1 | 1 | 队列中非第一个操作码字节 |

8086处理器工作时序

【指令周期】

在冯诺依曼计算机中,将CPU取得并执行一条指令所花的时间定义为一个指令周期。

【总线周期】

CPU通过系统总线对主存或I/O设备进行一次读/写访问所需的时间。8086 CPU的一个总线周期由 4 个时钟周期(T1、T2、T3、T4)组成。

【基本总线时序】

等待周期 TWAIT 一般插入到 T3 后面

I. 写总线周期(Concise Mode)

T1: Load Address

T1: Select Interface

T2: Load Data

AD0∼AD15⟹D0∼D15

T3: Continue T2

READY信号:解决主存或I/O接口实际写入时间长于CPU提供的时间的问题

T4: Restore States

II. 读总线周期(Concise Mode)——对比写总线周期

DT/¯R

III. 中断响应周期(Concise Mode)

Response Conditions:

INTA Period: from T2 to T4

First INTA Period:

Second INTA Period:

8086系统总线的形成

系统总线:地址总线(AB)、数据总线(DB)、控制总线(CB)

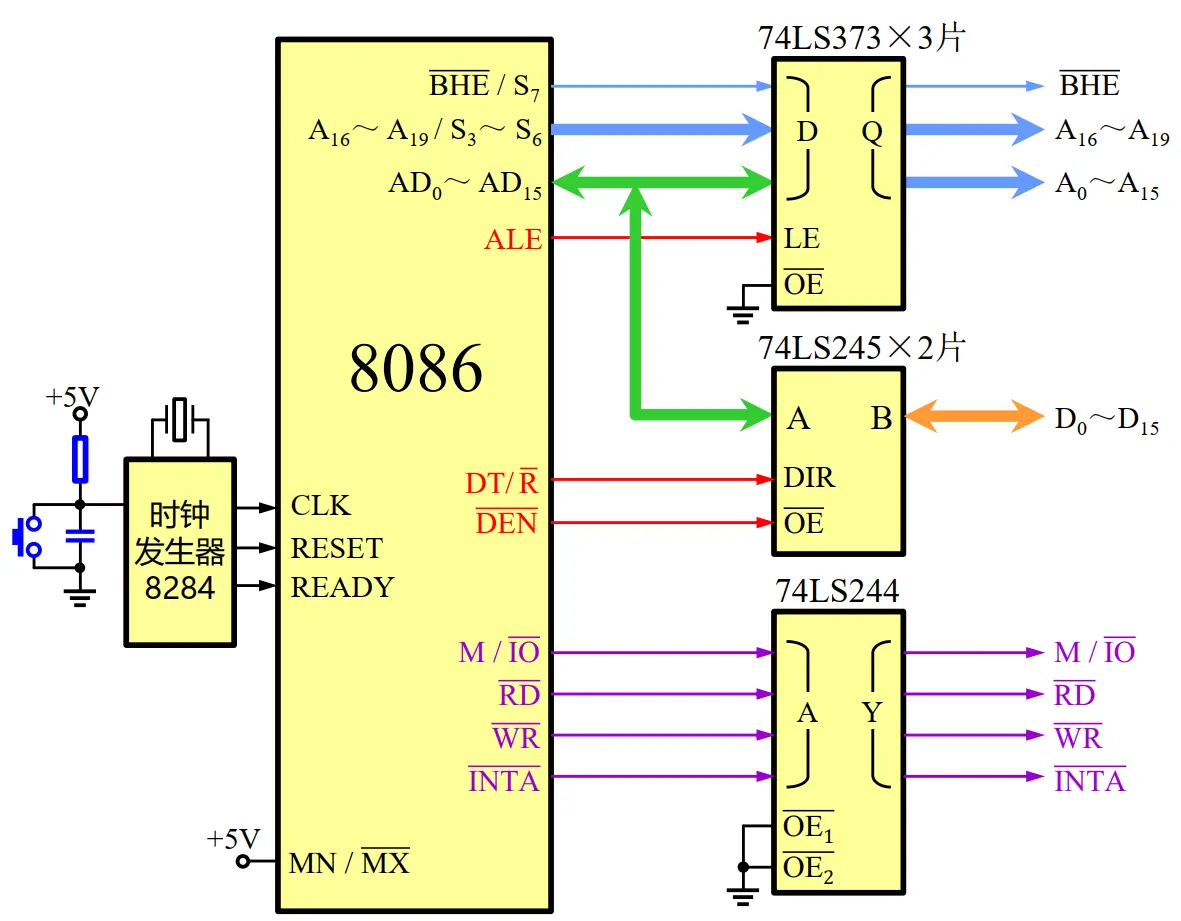

I. 最小模式的系统总线

8086 CPU 工作在最小模式下,系统总线信号全部来自CPU

- 地址总线 AB: A0∼A19、¯BHE/S7 (ALE信号由 8086 CPU 提供)

- 双向数据总线 DB: D0∼D15

- 控制总线 CB: 8086 CPU 在最小模式下提供的所有控制信号

8086在最小模式下的系统总线形成

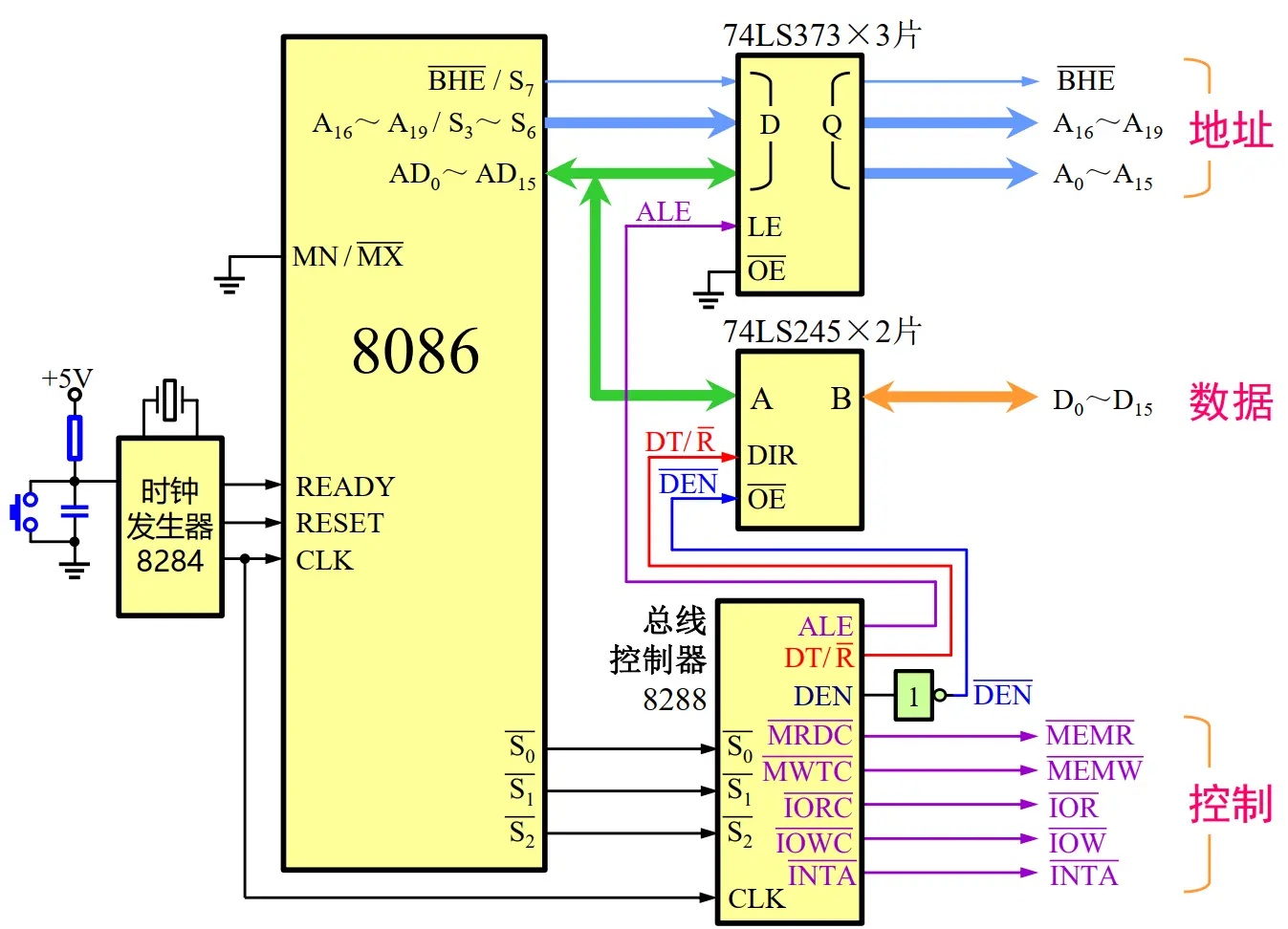

II. 最大模式的系统总线

8086 CPU 工作在最大模式下,系统总线信号来自 CPU 和总线控制器 8288

- 地址总线 AB: A0∼A19、¯BHE/S7 (ALE信号由总线控制器 8288 提供)

- 双向数据总线 DB: D0∼D15

- 控制总线 CB: 最大模式下的控制总线信号由 8086 CPU 和总线控制器 8288 共同提供

8086在最大模式下的系统总线形成

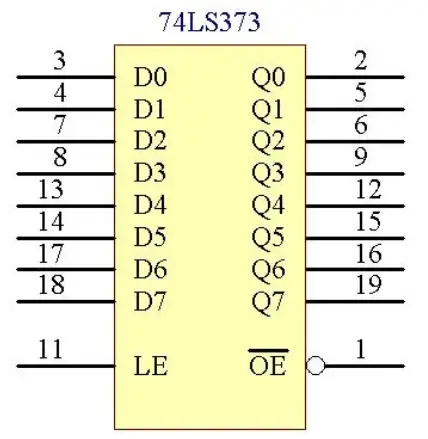

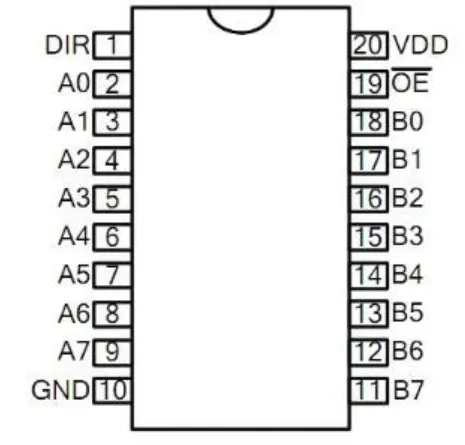

III. 常用芯片引脚分布

【74LS373——8位锁存器】 74LS373芯片引脚分布

【74LS245——双向驱动器】 74LS245芯片引脚分布

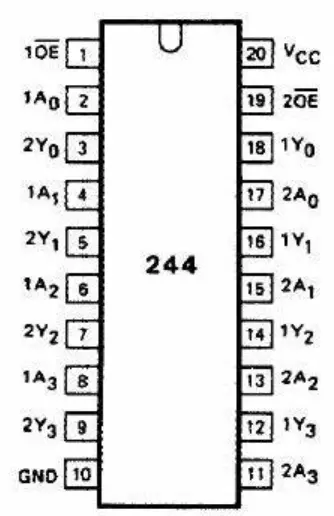

【74LS244——单向驱动器】 74LS244芯片引脚分布

第三章 Intel 处理器指令系统及汇编语言

第一讲 指令寻址方式

操作数的寻址方式

指令格式:操作码+操作数(操作数本身/操作数地址/地址的一部分/操作数地址的指针/其他操作数信息)

- 立即寻址

指令格式:操作数包含在指令中

存储形式:操作码 [n]+imL[n+1]+imH[n+2](小端存储)

存储位置:与操作码一起存放在代码段区域中

指令用途:主要用来给寄存器/存储器赋初值

- 直接寻址

指令格式:16位段内偏移地址包含在指令中

存储形式:操作码 [n]+offsetL[n+1]+offsetH[n+2](小端存储)

存储位置:与操作码一起存放在代码段区域中

- 寄存器寻址

指令格式:操作数包含在CPU的内部寄存器中

存储位置:存放在寄存器中

- 寄存器间接寻址

指令格式:操作数的16位段内偏移地址存放在 SI/DI/BP/BX 中, 其中 SI/DI/BX 间接寻址时操作数通常存放在现行数据段中; BP 间接寻址时操作数存放在堆栈段中

存储位置:操作数存放在存储器中

- 寄存器相对寻址

指令格式:指令中存放段内偏移地址的寄存器 SI/DI/BX/BP + 8/16 位带符号相对地址偏移量 DISP

存储位置:操作数存放在存储器中

- 基址、变址寻址

指令格式:指令指定一个基址寄存器 BX/BP 和一个变址寄存器 SI/DI

存储位置:操作数存放在存储器中

- 基址、变址、相对寻址

指令格式:指令指定一个基址寄存器 BX/BP、一个变址寄存器 SI/DI 和相对偏移地址 DISP

存储位置:操作数存放在内存中

- 隐含寻址

指令格式:操作数的地址隐含在指令操作码中

转移地址的寻址方式

- 段内直接寻址(相对寻址)

指令格式:指令指明8位或16位带符号相对地址偏移量 DISP(补码表示)

指令说明:相对寻址指的是在程序计数器的基础上加上偏移量进行相对位移

- 段内间接寻址

指令格式:指令指明存放段内偏移地址的寄存器或存储器单元地址,按指令码中规定的寻址方式取得转移地址

指令说明:间接寻址指的是通过寄存器或存储器单元获取得到新的段内偏移地址赋值给程序计数器而段地址不变

- 段间直接寻址

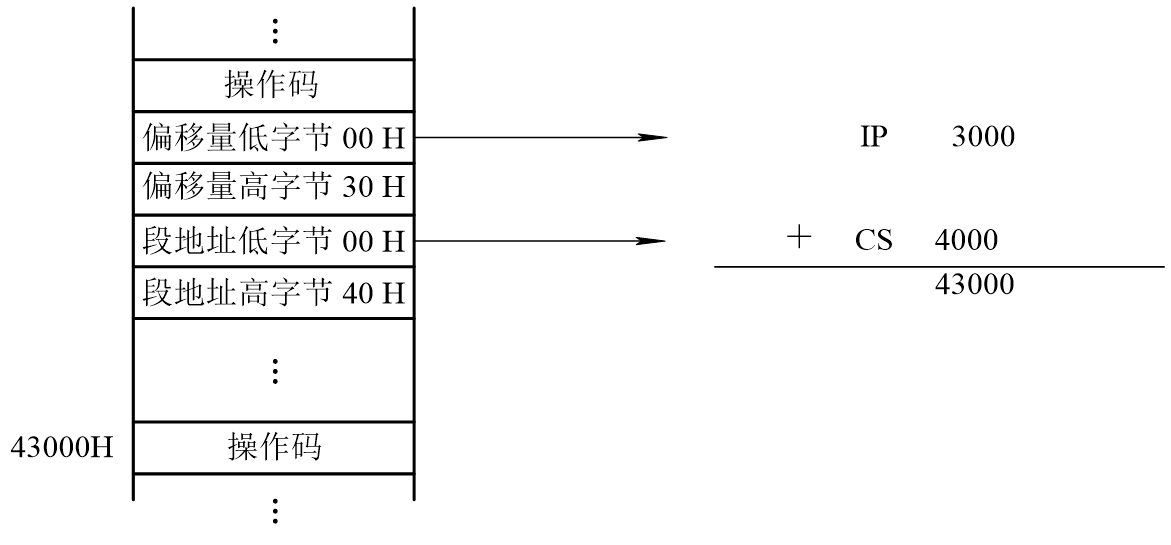

指令格式:指令码指明段地址和偏移地址所在存储单元的首地址: OPRD (标号或立即数, 标号会在编译时由 CPU 转换为对应的地址) 段间直接寻址地址对应关系

指令说明:操作码后连续四个字节,低字表示段内转移地址,高字表示段地址,直接赋值给 IP, CS (直接寻址)

- 段间间接寻址

指令格式:依据指令码寻址方式确定存储单元的首地址,前两个单元:段内偏移地址,后两个单元:段地址

指令说明:需要确定段地址 (16位) 和段内偏移地址 (16位) 32 位信息,只适用于存储器寻址方式

第二讲 汇编语言

- 引言:汇编语言的用途

- 嵌入式系统中,程序大小和运行速度需要高度优化

- 设计驱动程序、操作系统内核以及编译程序

- 高级语言中嵌入汇编

- 汇编语言的访问层次

- OS函数

- BIOS功能(一组固化到计算机内主板上一个ROM芯片上的程序,保存着计算机最重要的基本输入输出的程序、开机后自检程序和系统自启动程序)

- 硬件

汇编语言程序结构

- 操作系统装入程序:初始化CS为正确的代码段地址,初始化SS为正确的堆栈段地址

- ASSUME 伪指令:指明段与段寄存器的对应关系

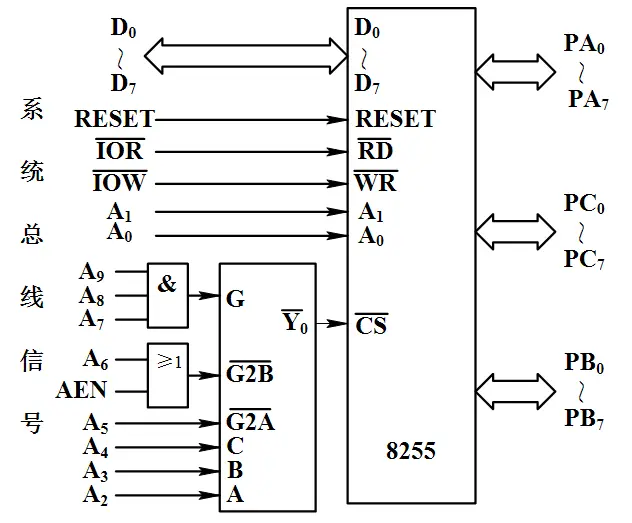

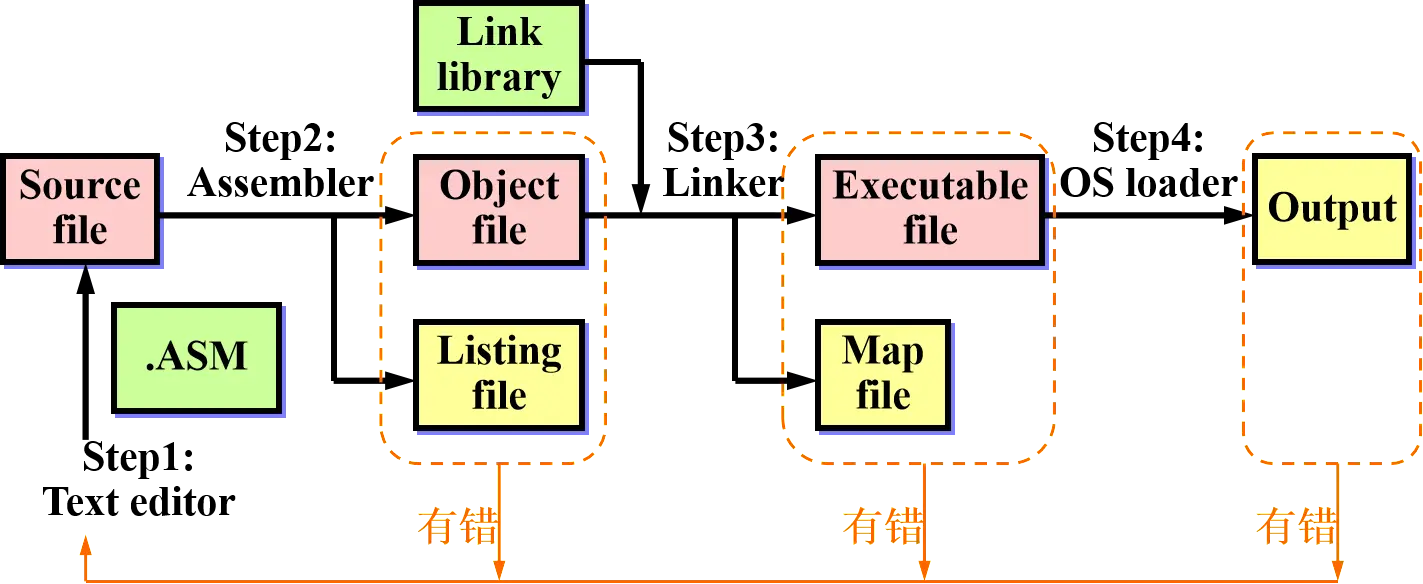

- 编译、链接和运行程序

编译、链接和运行程序

汇编语言基本元素

- 整数常量

- 保留字

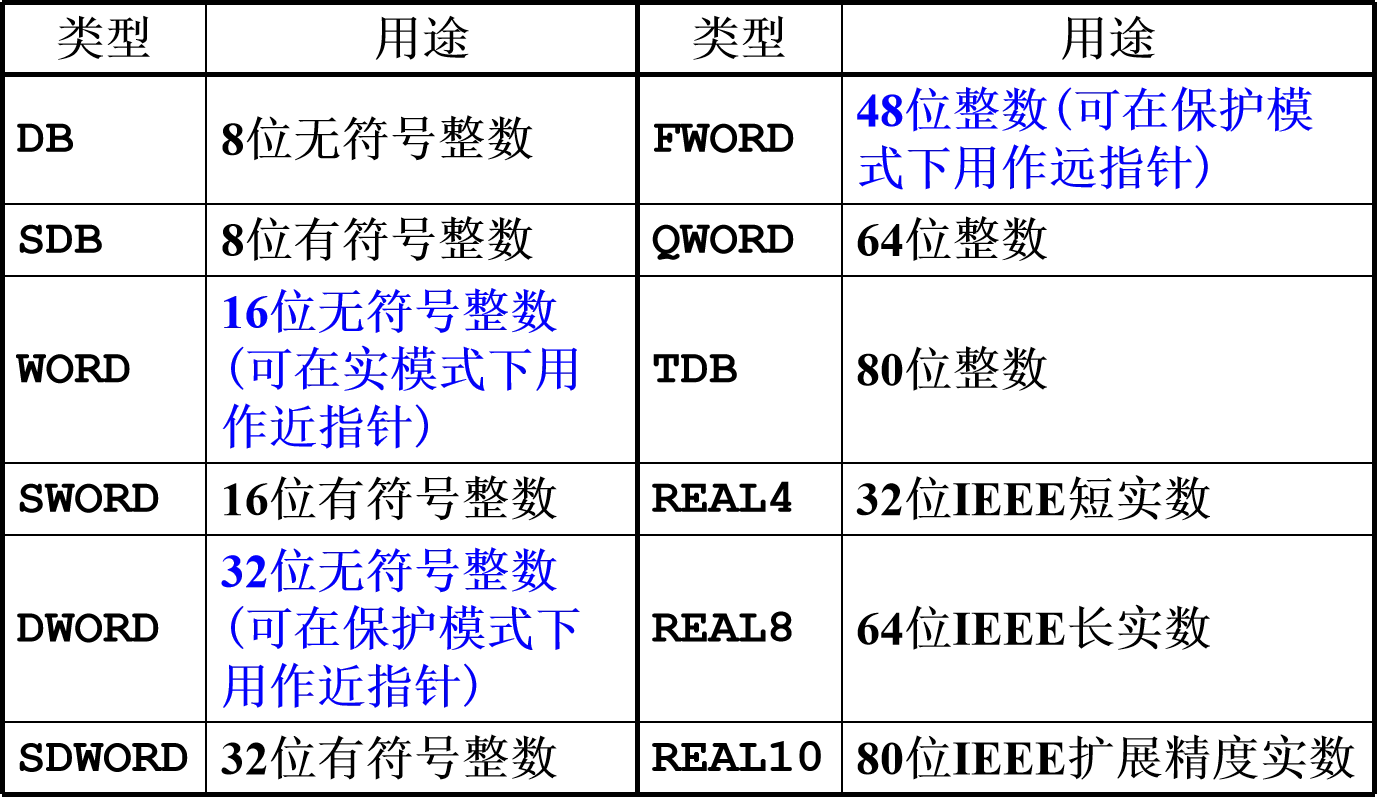

- 定义数据伪指令

定义数据伪指令

- 符号常量伪指令

不占用任何实际的存储空间 - 操作符

- 定义数据伪指令

第三讲 指令系统

数据传送指令

操作数类型

- 立即数 (Immediate)

- 寄存器操作数 (Register)

- 内存操作数 (Memory)

数据传送指令

MOV

MOVZX (move with zero-extend, 高位填充 0)

MOVSX (move with sign-extend, 高位填充符号位)

字节-字转换命令

XCHG (exchange data)

堆栈操作指令概述

- 以字 (16 位) 为单位进行数据压入和弹出操作,但是存储单元仍是 8 位

- SS 指示堆栈段的段基址,SP 始终指向堆栈的顶部,即最后一个存储单元

- 进栈方向从高地址向低地址发展 (SP 的初值决定了所用堆栈区的大小)

堆栈用途

- 作为临时保存区域,保存局部变量

- 备份寄存器状态,以便恢复其原始值

- CALL 指令执行时,CPU 用堆栈保存当前过程的返回地址

- 调用过程中,通过堆栈传递参数

PUSH

POP

PUSHFD (32 位程序)

POPFD (32 位程序)

PUSHF (实地址模式)

POPF (实地址模式)

PUSHAD (Push All Data)

POPAD (Pop All Data)

PUSHA (80286 处理器)

POPA (80286 处理器)

LEA (Load Effective Address)

LDS (Load DS)

LES (Load ES)

Special Rules(LEA, LDS, LES):

- 源操作数必须是一个内存操作数

- 目的操作数必须是一个 16 位的通用寄存器

算术运算类指令

加法和减法指令

INC

DEC

ADD

ADC

SUB

SBB

NEG

乘法和除法指令

MUL

IMUL

DIV

IDIV

CBW

- 将AL中的符号位扩展到AH

CWD

- 将AX中的符号位扩展到DX

CDQ

- 将EAX中的符号位扩展到EDX

溢出

- 商太大,目的操作数无法容纳 -> 使用32位除数

- 除数 = 0 → 跳过,不执行

逻辑运算和移位指令

逻辑运算类指令

- AND

- OR

- XOR

- 寄存器清零

- NOT

比较测试指令

CMP

TEST

控制转移指令

转移指令概述

- 实质: 改变 IP(或 CS) 的内容

- 所有转移指令不会影响标志位

无条件转移指令

JMP

- JMP disp (段内直接转移)

- CS 保持不变, 指令中 8/16 位偏移量加到 IP

- JMP reg/mem (段内间接转移)

- CS 保持不变, reg/mem 中的 16 位偏移地址送到 IP

- 16 位偏移地址指的是段内偏移地址,而不是相对于 IP 的偏移量

- JMP segment:offset (段间直接转移)

- 指令中的 16 位段地址和 16 位偏移地址送到 CS 和 IP (立即数)

- JMP mem32 (段间间接转移)

- mem32 中的 16 位段地址和 16 位偏移地址送到 CS 和 IP (两个相邻字)

- JMP disp (段内直接转移)

条件跳转指令

- 声明全局变量 (变量后面紧跟 “::”)

- 基于特定 CPU 标志值的跳转指令

助记符 标志位 标志值/跳转条件 JZ ZF(零标志位) 1 JNZ ZF(零标志位) 0 JC CF(进位标志位) 1 JNC CF(进位标志位) 0 JO OF(溢出标志位) 1 JNO OF(溢出标志位) 0 JS SF(符号标志位) 1 JNS SF(符号标志位) 0 JP PF(奇偶标志位) 1 JNP PF(奇偶标志位) 0

- 依据相等比较的跳转指令

- 指令格式:

- CMP LeftOp, RightOp

- Jxx Label

- 指令格式:

| 助记符 | 跳转条件 |

|---|---|

| JE | LeftOp = RightOp |

| JNE | LeftOp≠ RightOp |

| JCXZ | CX=0 |

| JECXZ | ECX=0 |

- 基于无符号整数比较结果的跳转指令

- 指令格式:

- CMP LeftOp, RightOp

- Jxx Label

- 指令助记: Z:zero, E:equal, A:above, B:below

- 指令格式:

| 助记符 | 跳转条件 |

|---|---|

| JA | LeftOp > RightOp |

| JAE | LeftOp >= RightOp |

| JB | LeftOp < RightOp |

| JBE | LeftOp <= RightOp |

| JNA | LeftOp <= RightOp |

| JNAE | LeftOp <= RightOp |

| JNB | LeftOp >= RightOp |

| JNBE | LeftOp >= RightOp |

- 基于有符号整数比较结果的跳转指令

- 指令格式:

- CMP LeftOp, RightOp

- Jxx Label

- 指令助记: Z:zero, E:equal, G:greater, L:less

- 指令格式:

| 助记符 | 跳转条件 |

|---|---|

| JG | LeftOp > RightOp |

| JGE | LeftOp >= RightOp |

| JL | LeftOp < RightOp |

| JLE | LeftOp <= RightOp |

| JNG | LeftOp <= RightOp |

| JNGE | LeftOp <= RightOp |

| JNL | LeftOp >= RightOp |

| JNLE | LeftOp >= RightOp |

循环指令

- LOOP

- LOOP Label

- 执行操作: (CX)−1 → CX

- 循环条件: (CX) ≠0 转至 Label 处循环执行

- 等价指令: DEC CX, JNZ Label

- 循环目的地址与当前地址相距范围:−128∼+127字节,机器指令平均 3 字节, 单词循环平均最多包含约 42 条指令

- LOOP Label

- LOOPZ (Loop if zero, Loop if equal)

- 指令等价:LOOPE

- 指令格式: LOOPZ Label

- 执行操作: (CX) −1→ CX

- 循环条件: (CX) ≠0∧ ZF =1

- LOOPNZ (Loop if not zero, Loop if not equal)

- 指令等价:LOOPNE

- 指令格式: LOOPNZ Label

- 执行操作: (CX) −1→ CX

- 循环条件: (CX) ≠0∧ ZF =0

- LOOP

移位和循环移位指令

助记符 指令含义 影响标志位 助记符 指令含义 影响标志位 助记符 指令含义 影响标志位 SHL 逻辑左移 CF,OF,PF,SF,ZF ROL 循环左移 CF,OF SHLD 双精度左移 CF,OF SHR 逻辑右移 CF,OF,PF,SF,ZF ROR 循环右移 CF,OF SHRD 双精度右移 CF,OF SAL 算术左移 CF,OF,PF,SF,ZF RCL 带进位的循环左移 CF,OF SAR 算术右移 CF,OF,PF,SF,ZF RCR 带进位的循环右移 CF,OF SHL/SAL

ROL

ROR

SHLD

- 至少是Intel 386处理器

- 指令格式: SHLD DEST, SRC, CL/imm8

- 功能: 将目的操作数左移指定的位数,低位空出来的位用源操作数的高位填充

- 影响标志: SF, ZF, AF, PF, CF

SHRD

- 至少是Intel 386处理器

- 指令格式: SHRD DEST, SRC, CL/imm8

- 功能: 将目的操作数右移指定的位数,高位空出来的位用源操作数的低位填充

- 影响标志: SF, ZF, AF, PF, CF

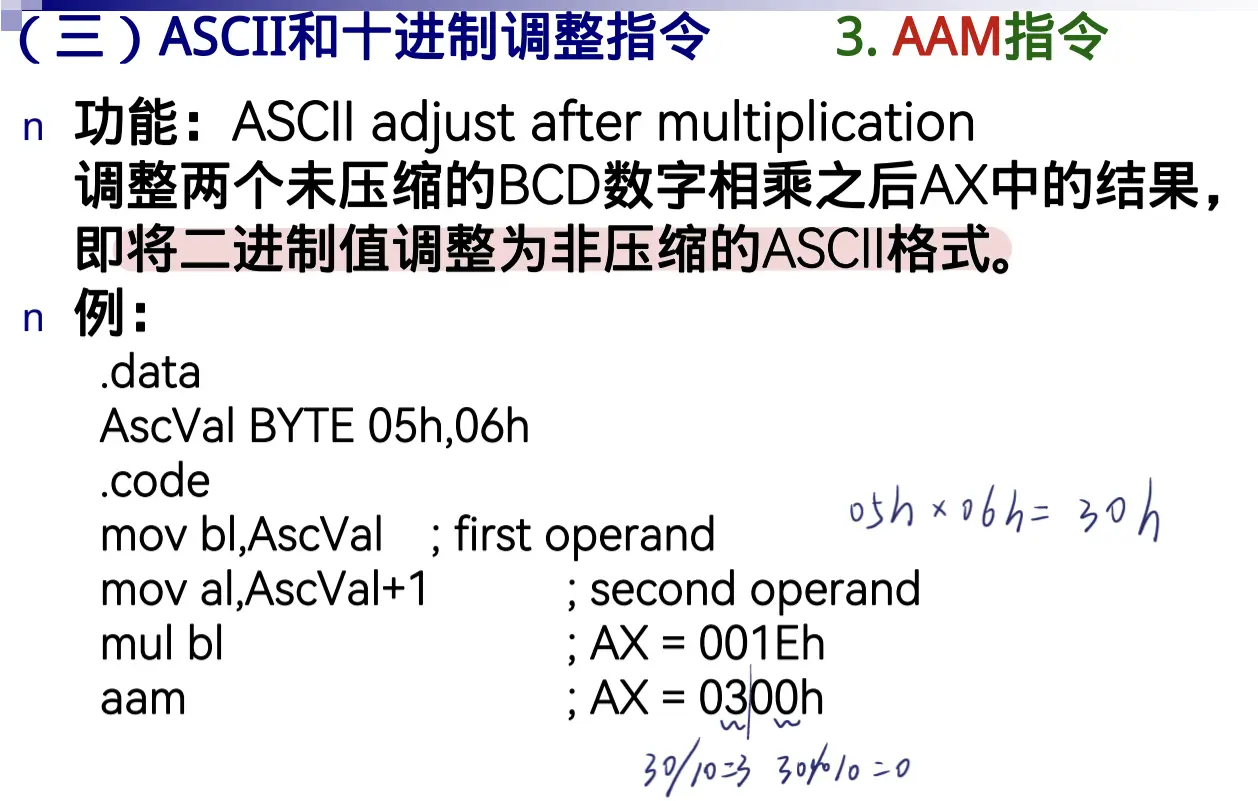

ASCII和十进制调整指令

- ASCII

- 十进制

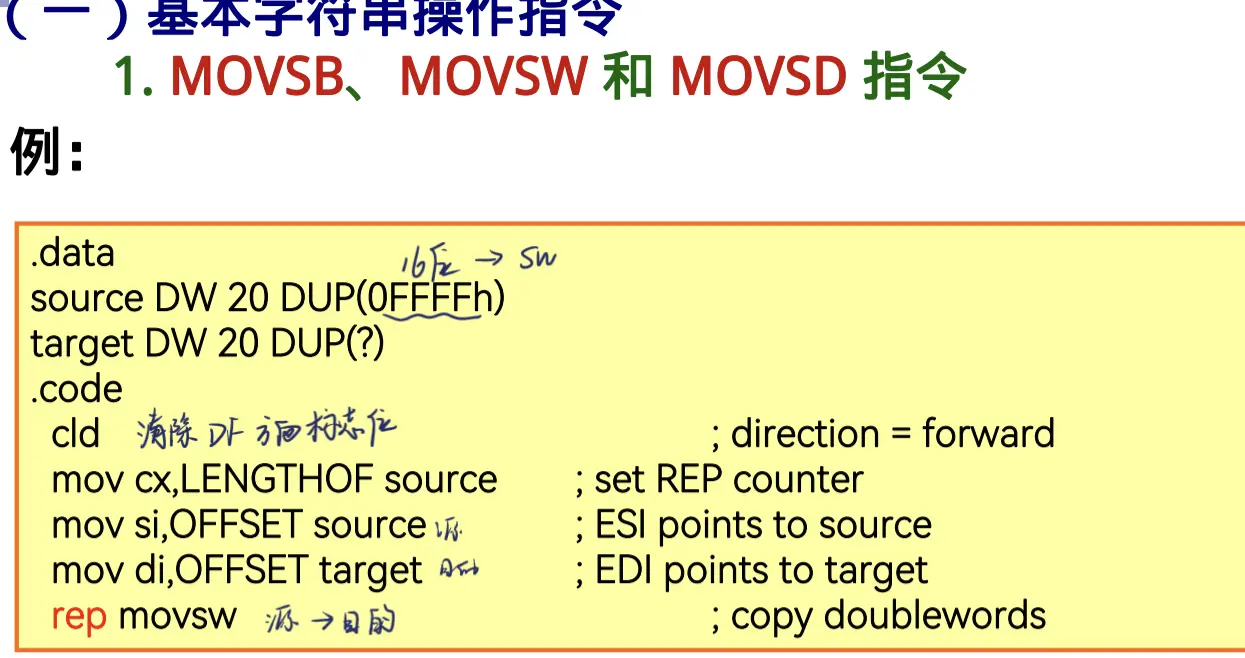

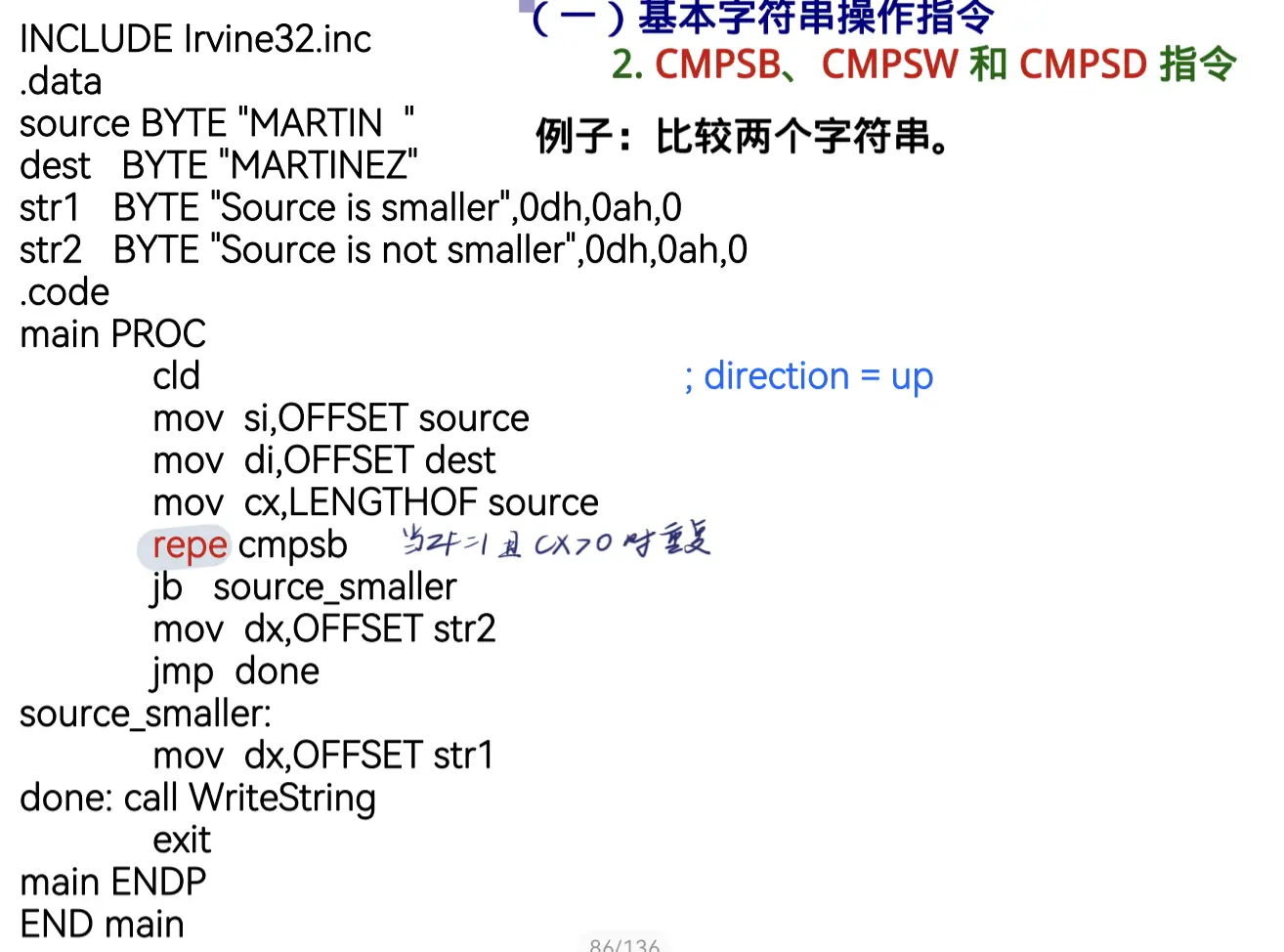

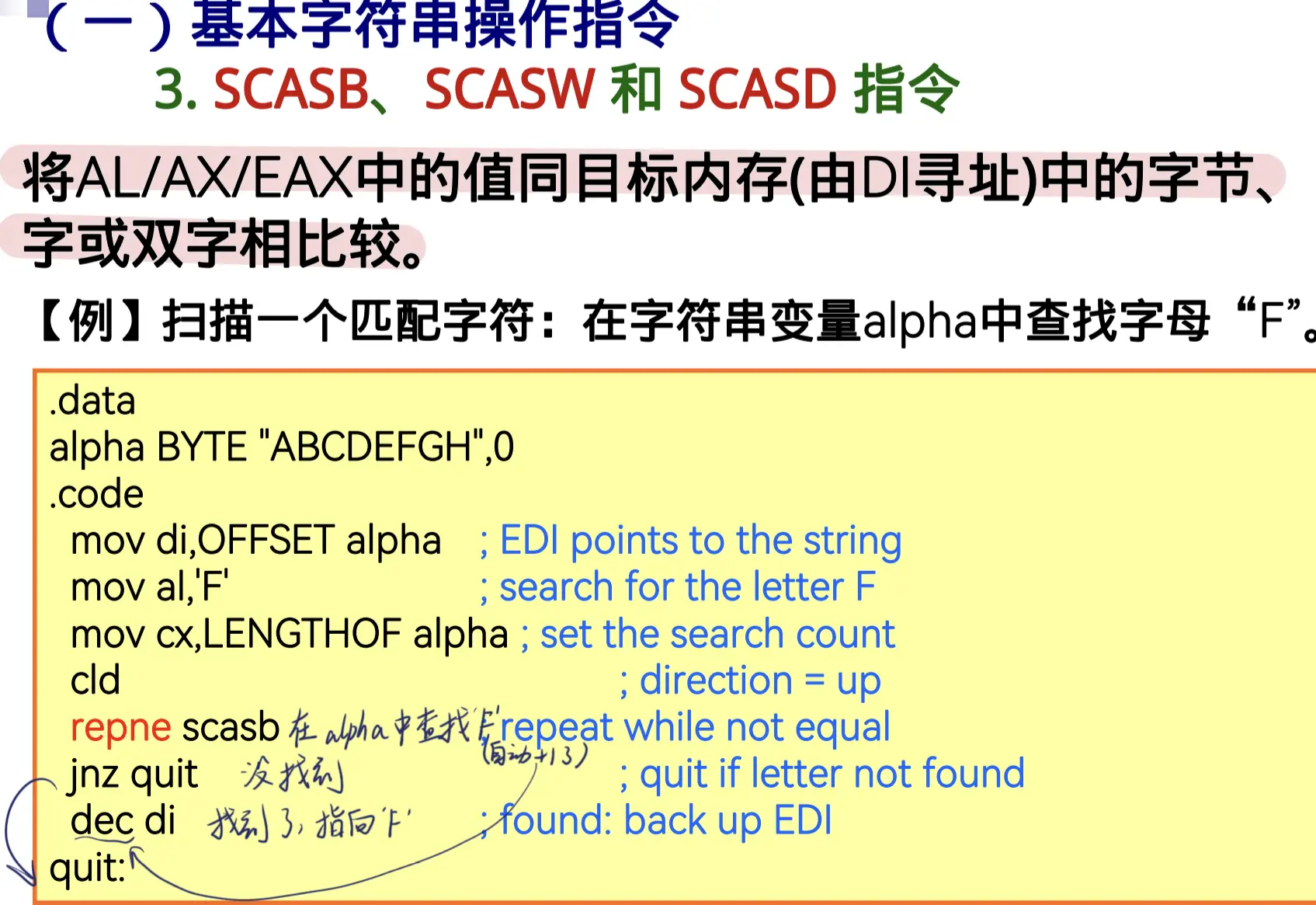

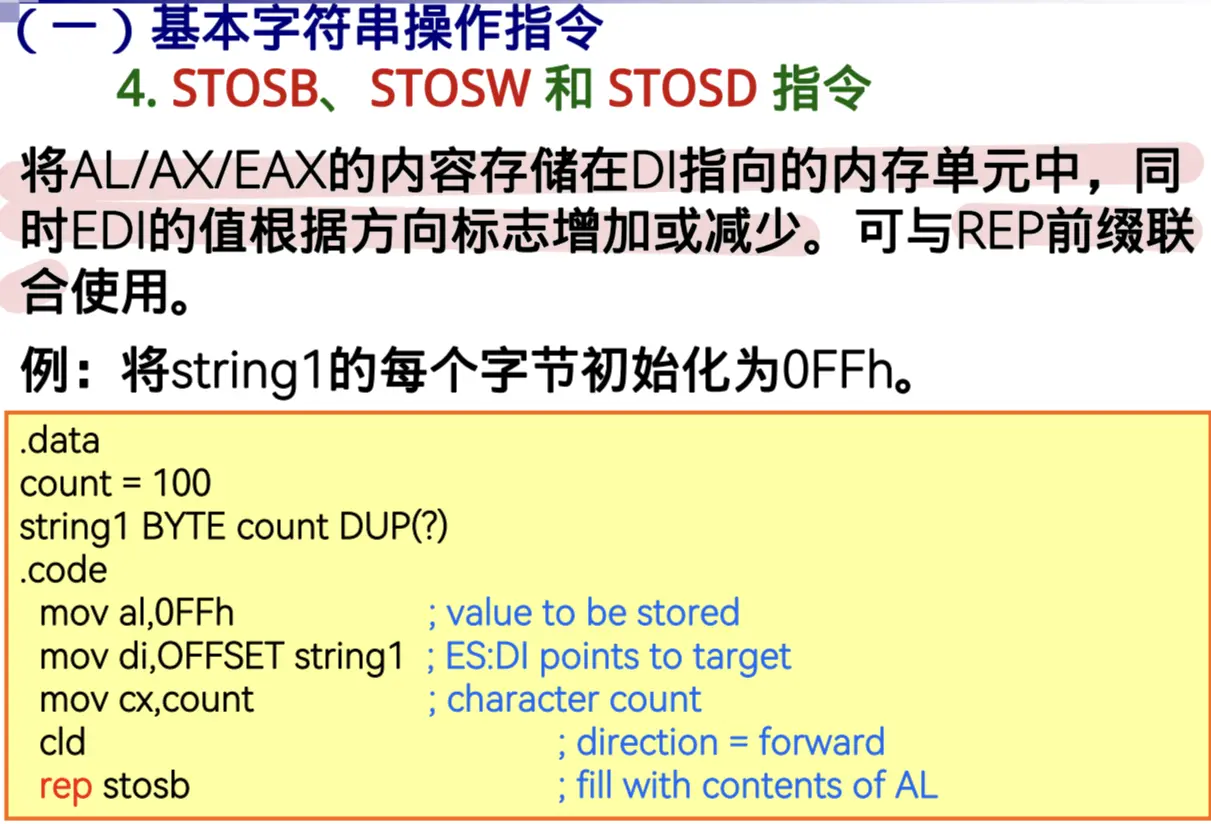

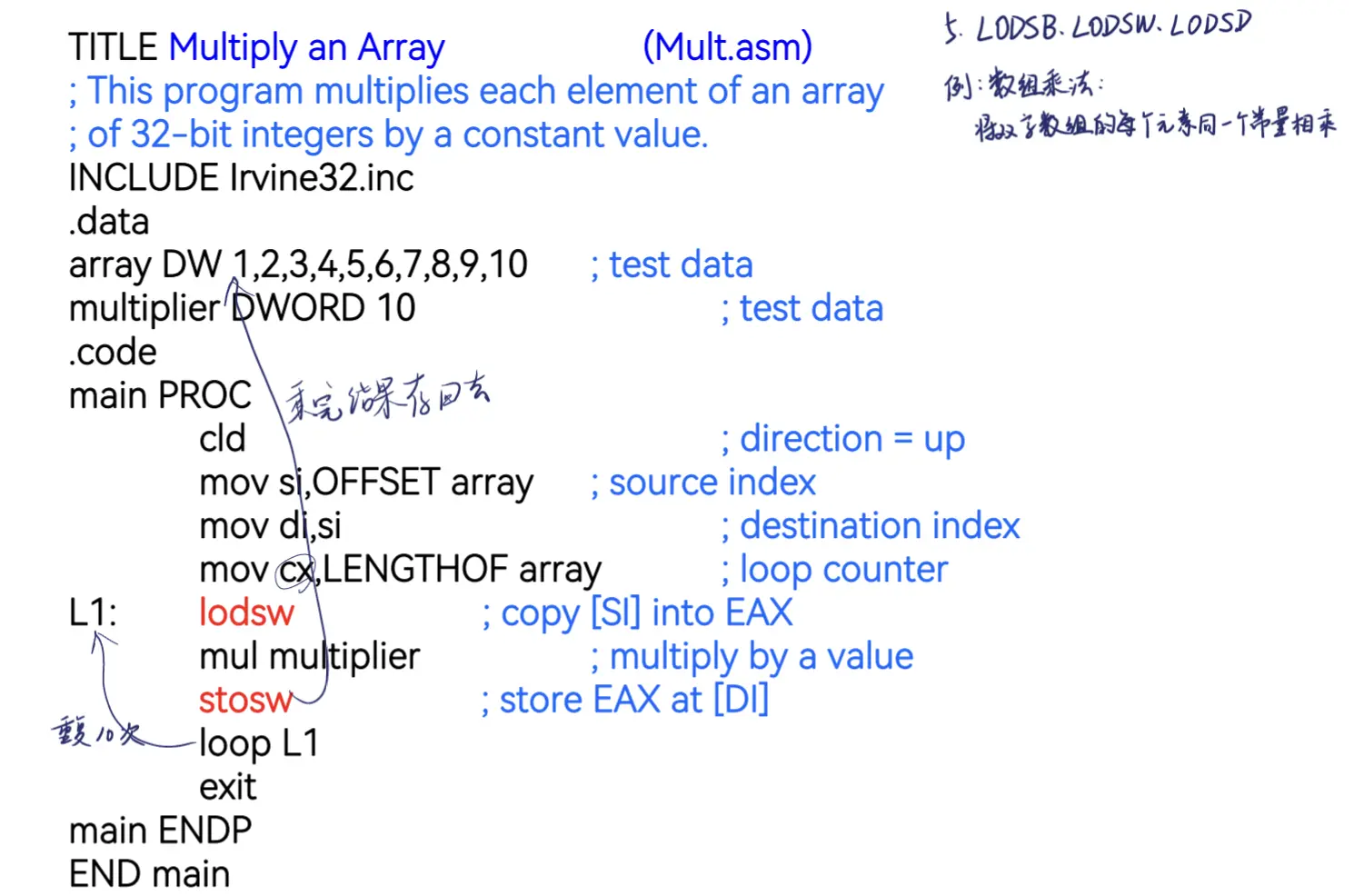

字符串操作指令

寻址方式

- 源操作数指针 DS:SI

- 目的操作数指针 ES:DI

- SI是DS段中的偏移

- DI是ES段中的偏移

- ES ES通常开始时设为同样的段值

- SI DI的值会自动修改(方向标志位DF=0 增;DF=1 减;CLD 清除方向标志位,STD 设置方向标志位)

基本字符串指令

使用重复前缀

- REP

- 当CX>0时重复

- REPZ, REPE

- 当ZF=1且CX>0时重复

- REONZ, REPNE

- 当ZF=0且CX>0时重复

- 实现用一条指令处理整个数组

- REP

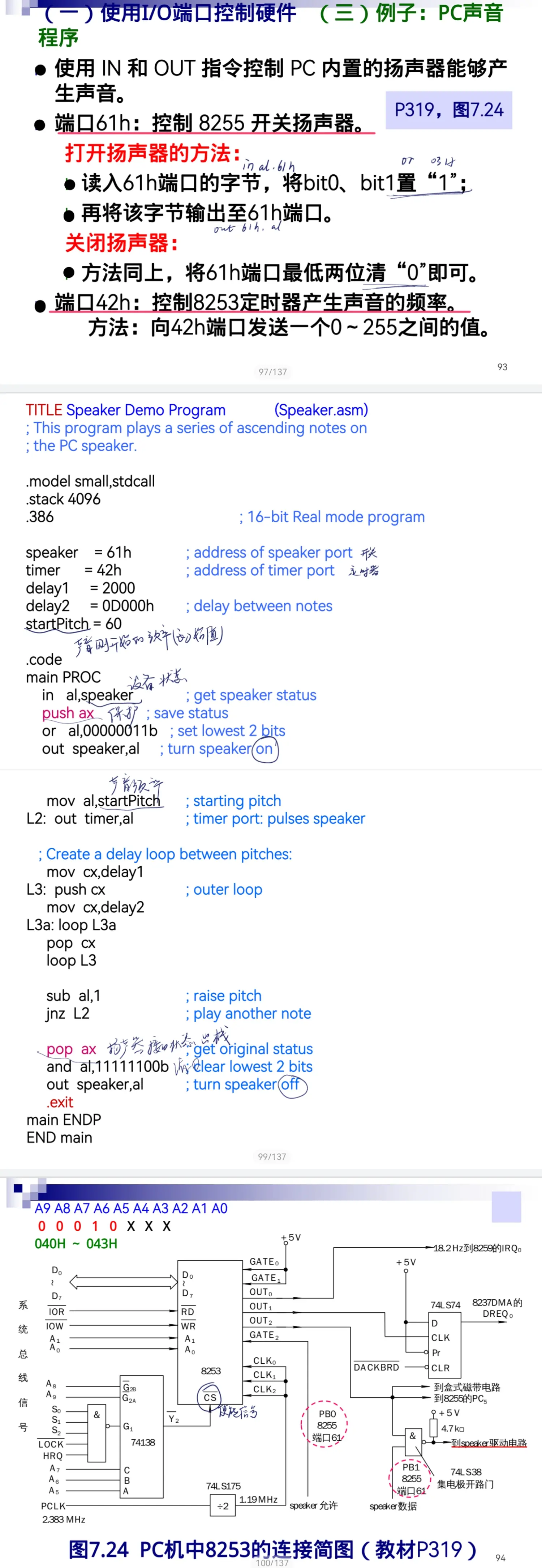

端口、过程与逻辑运算指令

使用I/O端口控制硬件

- 端口范围:0~FFFFh

- 端口作用:传送数据,返回状态,控制

- 指令

- IN 累加器,端口地址

- 累加器:AL\AX\EAX

- 端口地址

- 0~FFh之间的常量

- 包含0~FFFFh 之间值的DX寄存器

- OUT 端口地址,累加器

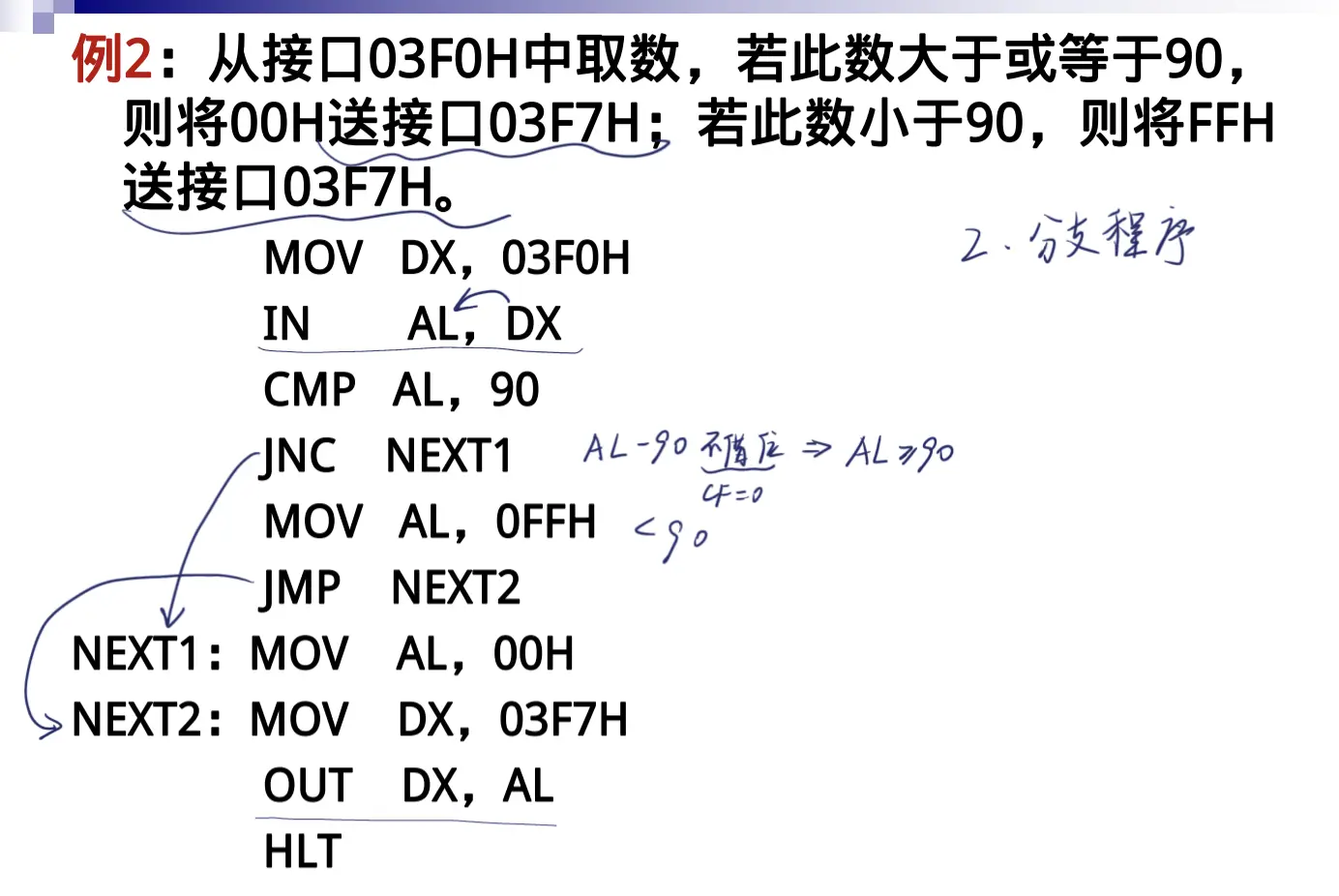

- 例题

i/o

- IN 累加器,端口地址

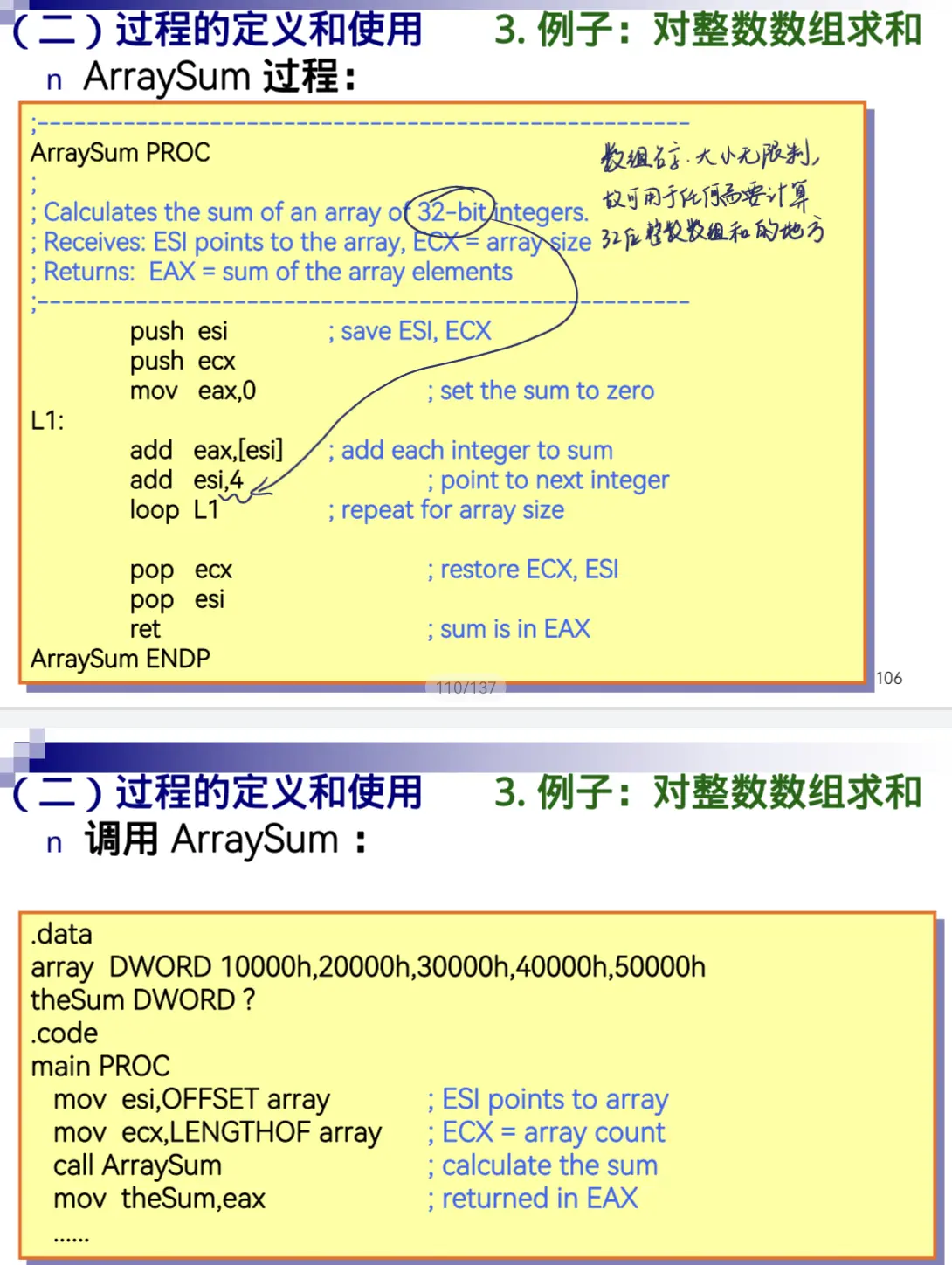

过程的定义和使用

- PROC伪指令

- CALL与RET指令

- CALL指令执行时,处理器自动完成压栈;RET指令执行时,处理器自动完成出栈

- 过程可以嵌套调用

- 局部标号(L1:)和全局标号(L1::)

- 例题

过程

逻辑运算指令

设置和清除单个CPU标志

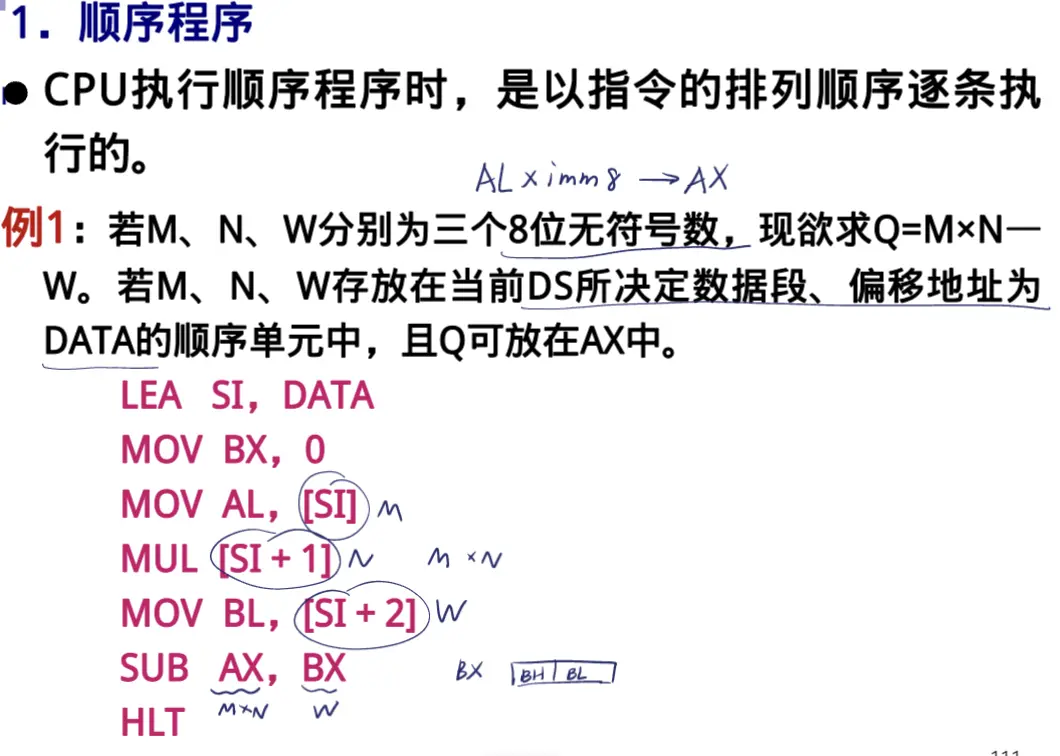

程序设计举例

顺序程序

- 例题

顺序程序

- 例题

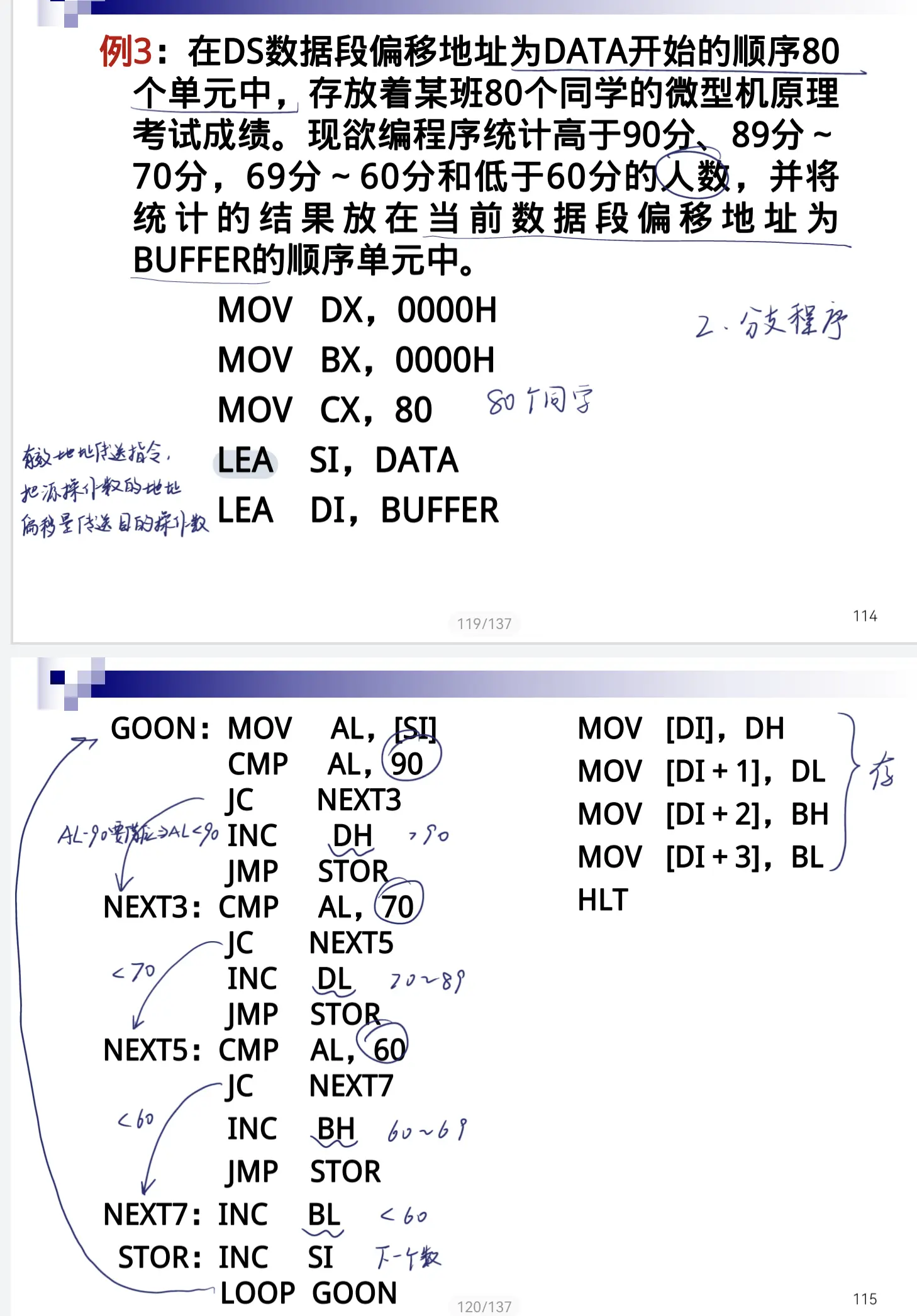

分支程序

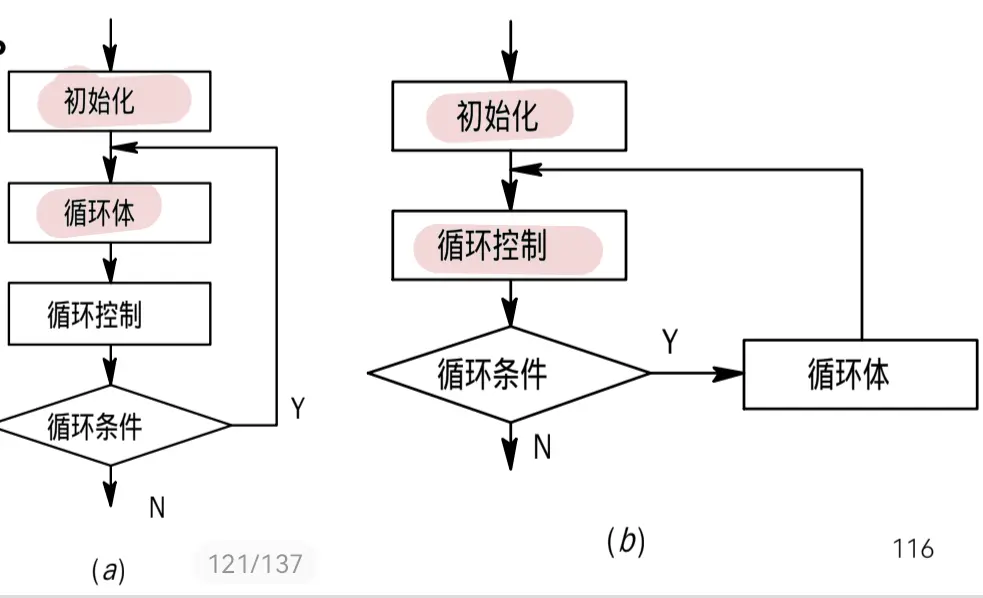

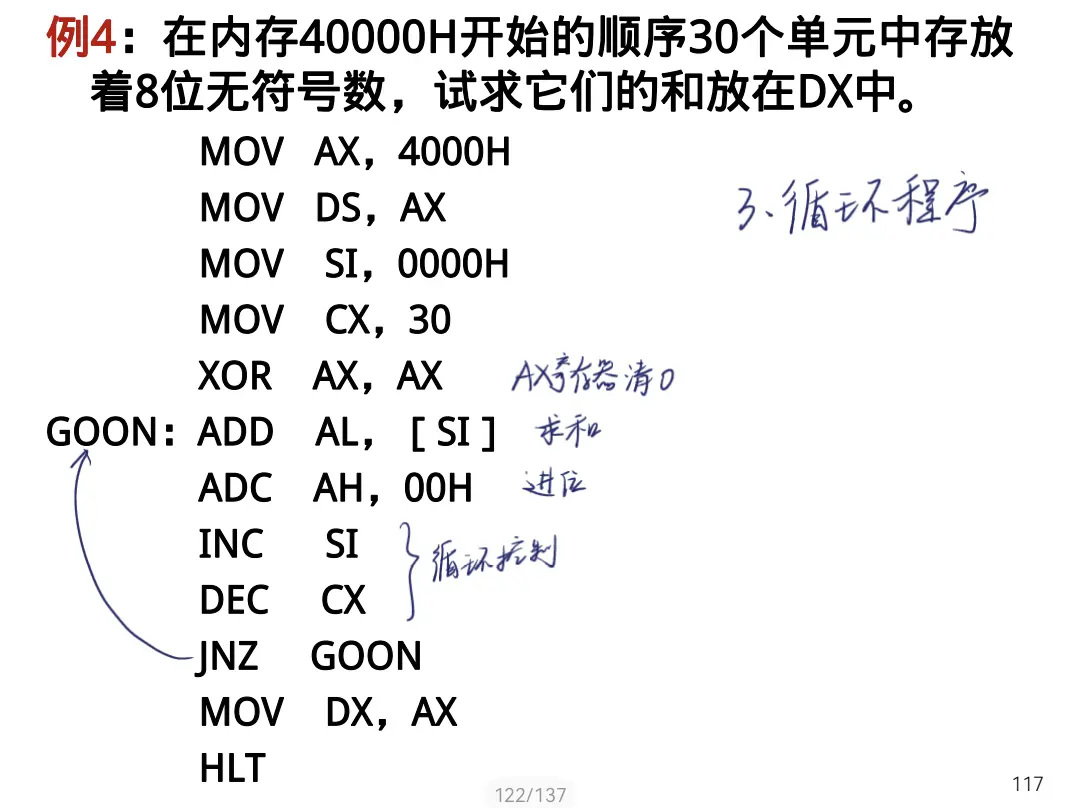

循环程序

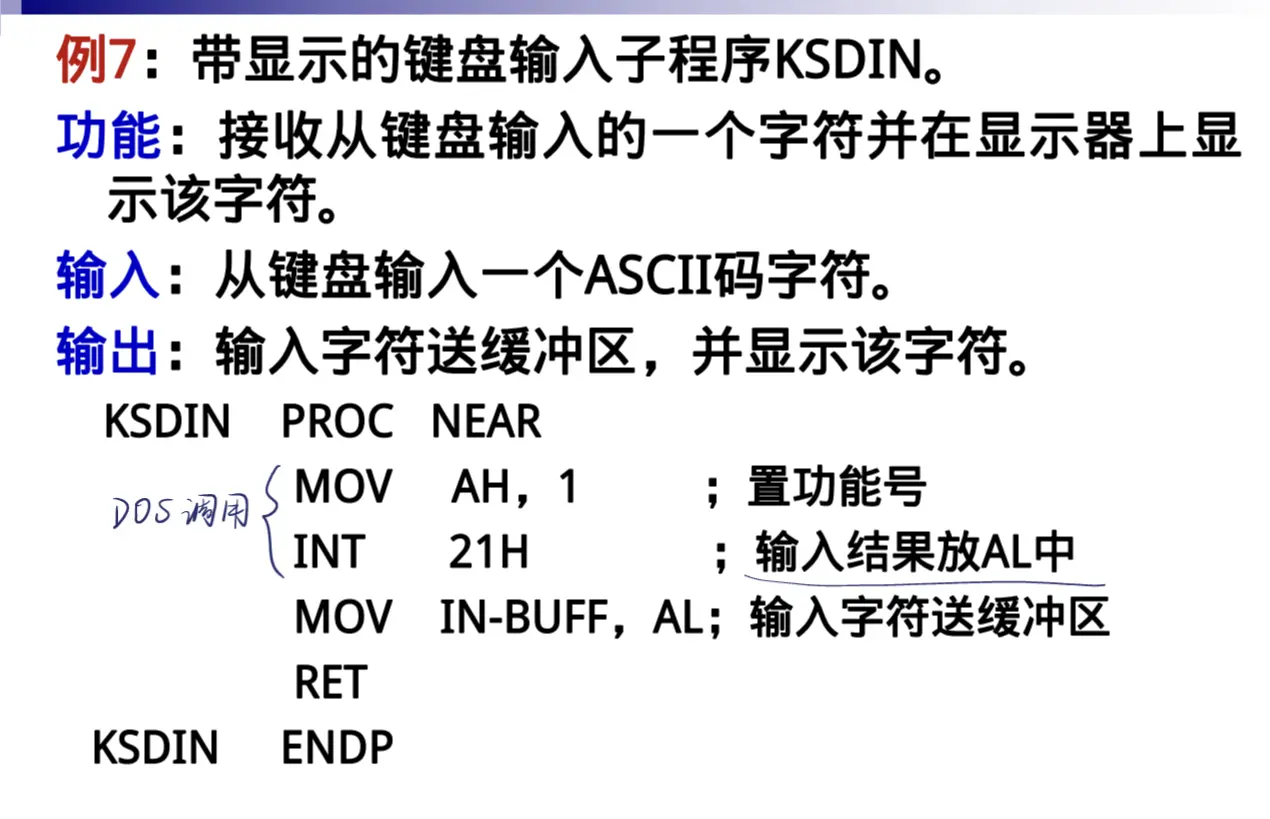

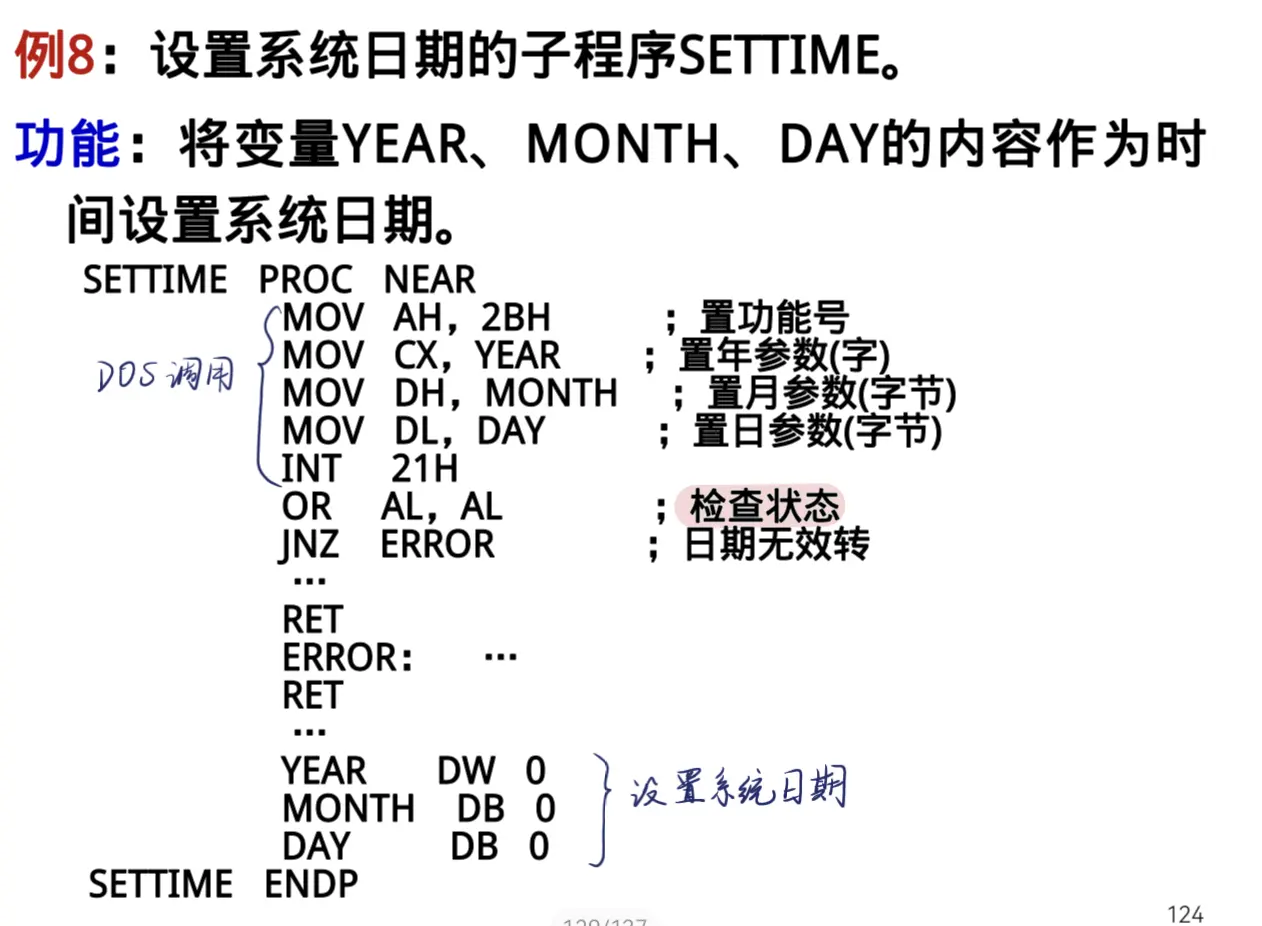

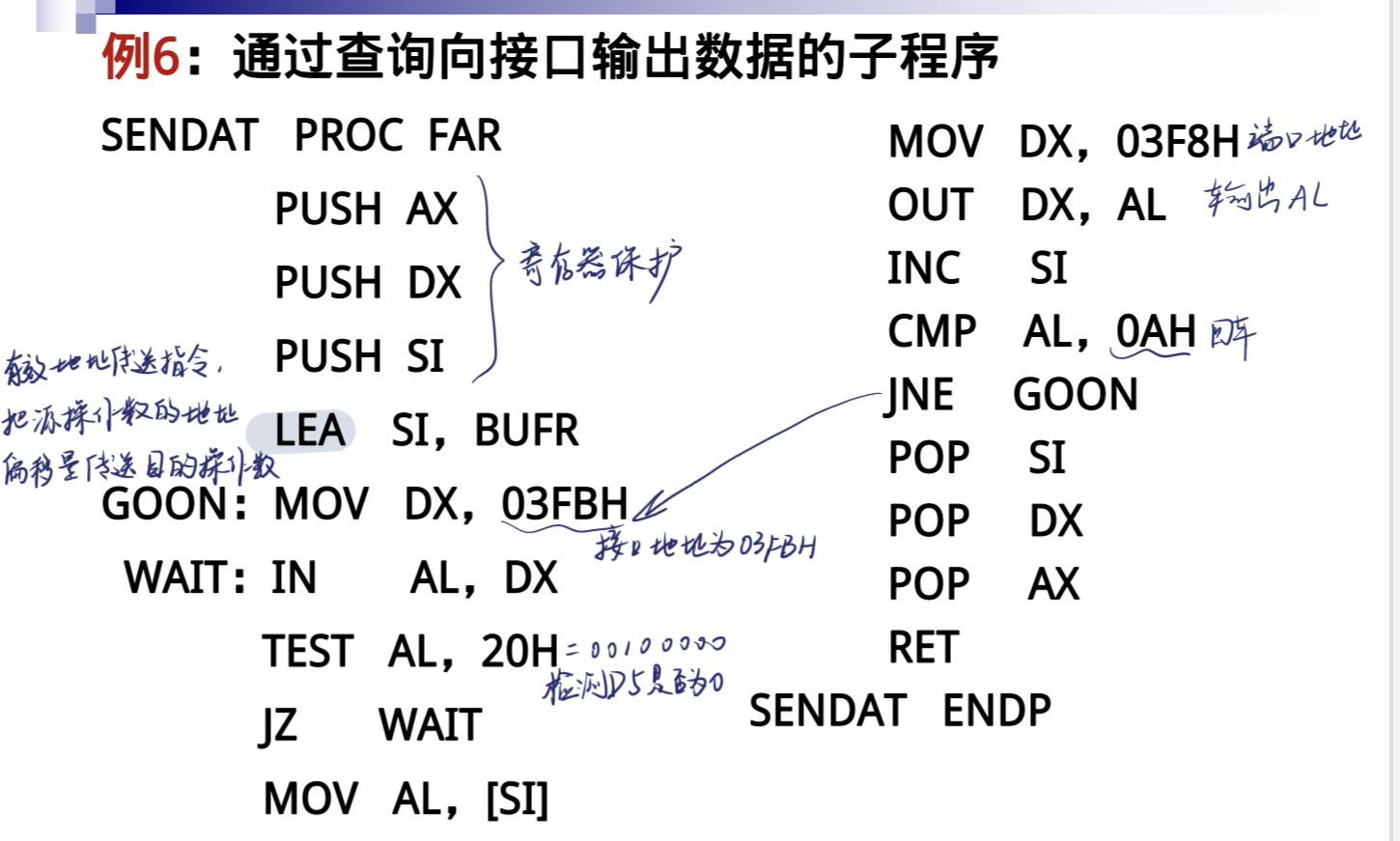

子程序

- 编写时应注意

- 如何调用和返回

- 入口条件和出口条件

- 寄存器、保护、影响哪些标志位、出错如何处理

- 参数传递

- 利用寄存器

- 利用内存单元

- 利用堆栈

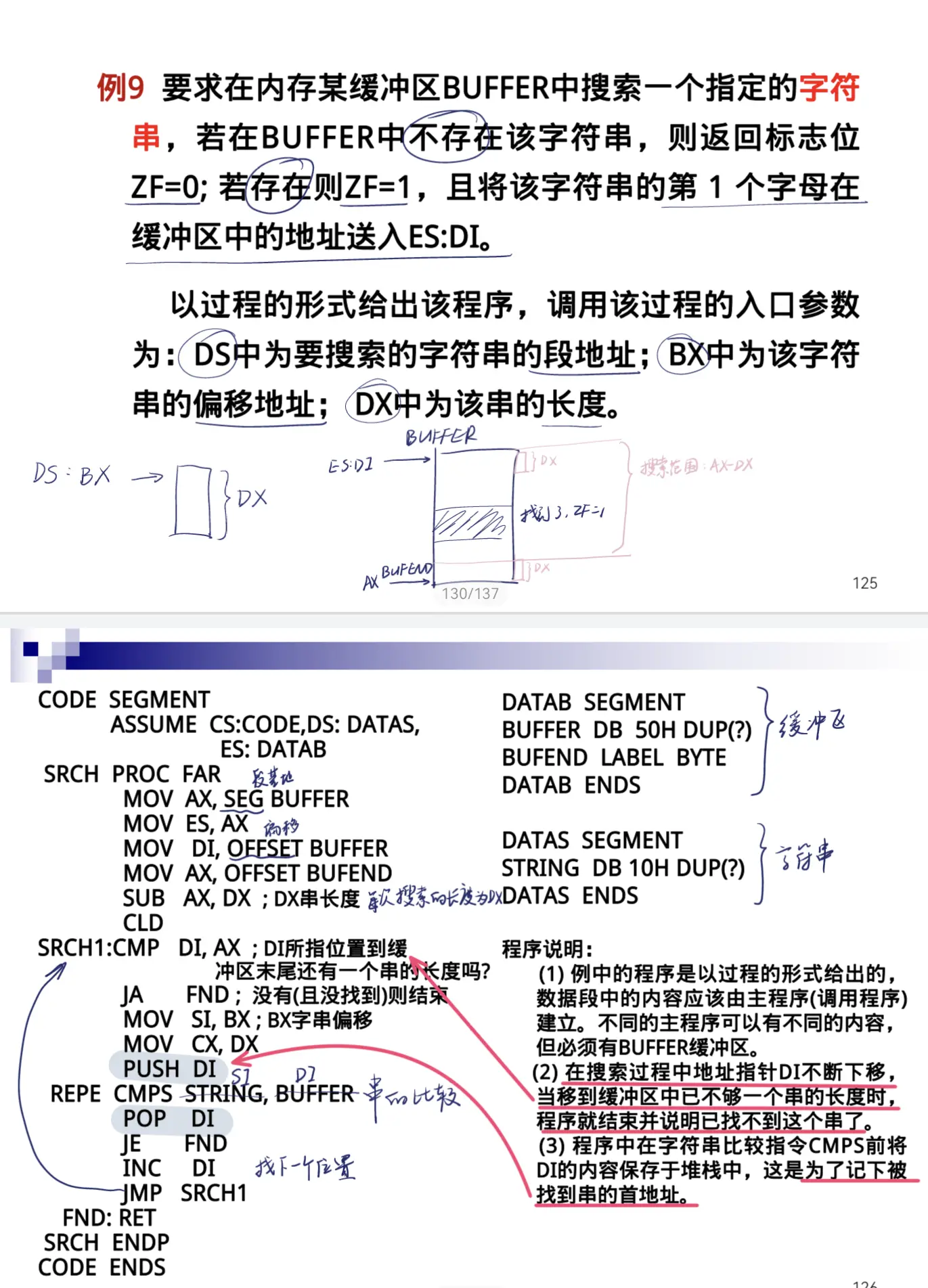

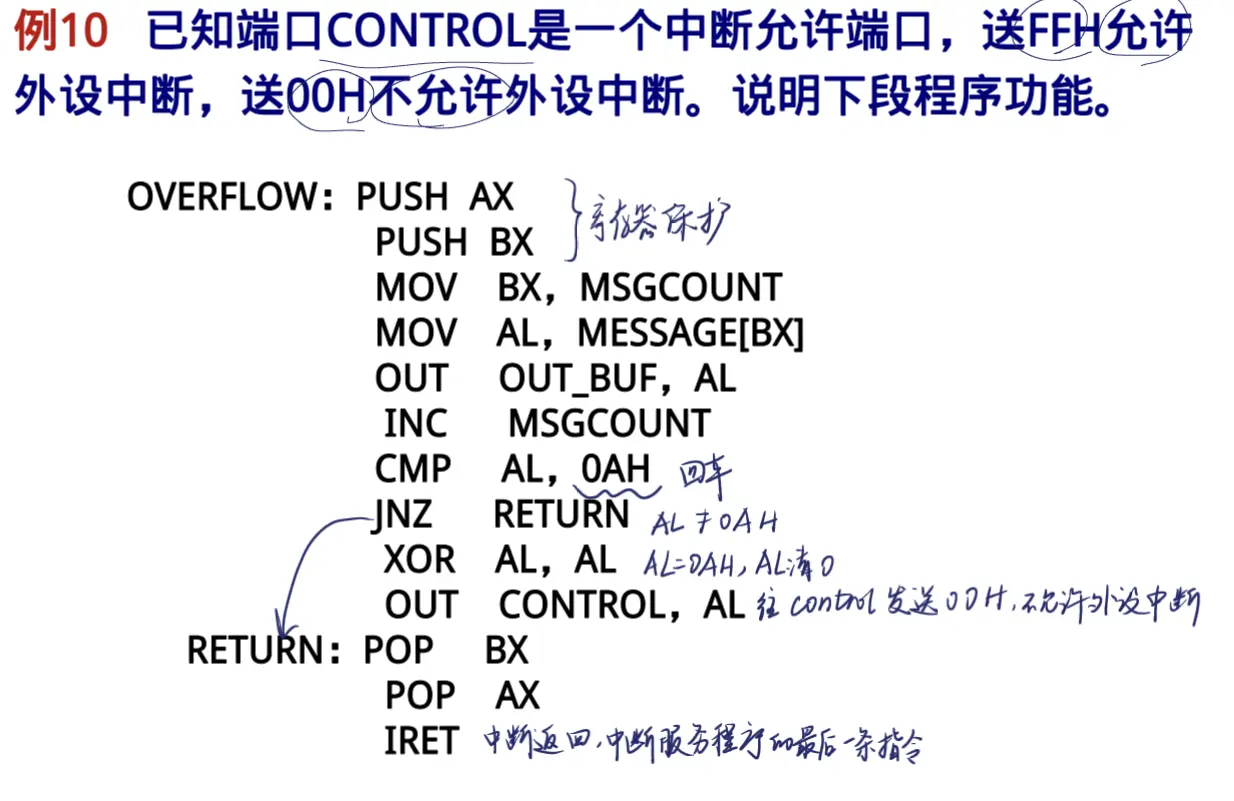

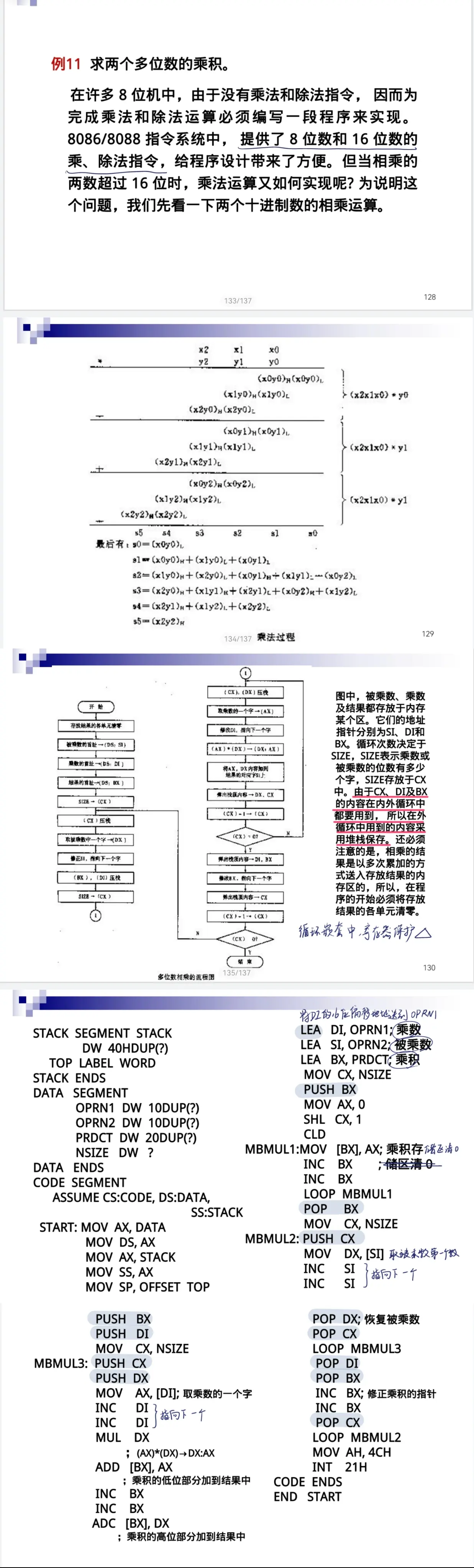

- 例题

子程序

- 编写时应注意

功能调用

Examples

1 | TITLE Summing an Array |

1 | TITLE Copying a String |

1 | TITLE Displaying Register Contents |

1 | TITLE Scanning an Array for Non-Zero Values |

1 | TITLE Scanning an Array |

1 | TITLE Compress BCD to ASCII |

第四章 总线技术

第一讲 总线概述

总线分类

内总线

PC机的内总线

- ISA总线(Industry Standard Architecture)

- PCI总线(Peripheral Component Interconnect Local Bus)

工控机的内总线

- STD总线

外总线

- RS232C

- SCSI

- USB总线

第二讲 总线的驱动与控制

总线竞争

- 同一总线上,同一时刻,有两个或以上的器件输出状态

- 防止总线竞争:用三态电路,严格控制逻辑

总线负载

- 直流负载

- 驱动器的高电平输出电流应不小于所有负载所需高电平输入电流之和

- 驱动器的低电平输出电流应不小于所有负载所需低电平输入电流之和

- 扇出数:驱动同门的个数,用 IOH / IIH 和 IOL / IIL,取二者的较小值

- 交流负载

- 对MOS电路,主要考虑电容负载

- 扇出数:输出门的负载电容 Cp / Cli

- 总扇出数:IOH / IIH 、 IOL / IIL 、 Cp / Cli,三者取最小值(理想情况)

总线驱动设计

- 克服总线负载效应:用驱动器和缓冲器

- 扇出能力大

- 延时可忽略

- 噪声容限较高

- 几种常用芯片(防止总线竞争)

- 单向驱动器(三态输出)(224)

- 双向驱动器(三态输出)(245)

- DIR = 0,读;DIR = 1,写

- 锁存器(三态输出)(373)

- 总线驱动设计

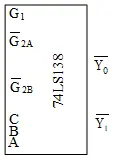

- 内存板:20位地址(¯MEMR 、 ¯MEMW),接口板:16位地址(¯IOR 、 ¯IOW)

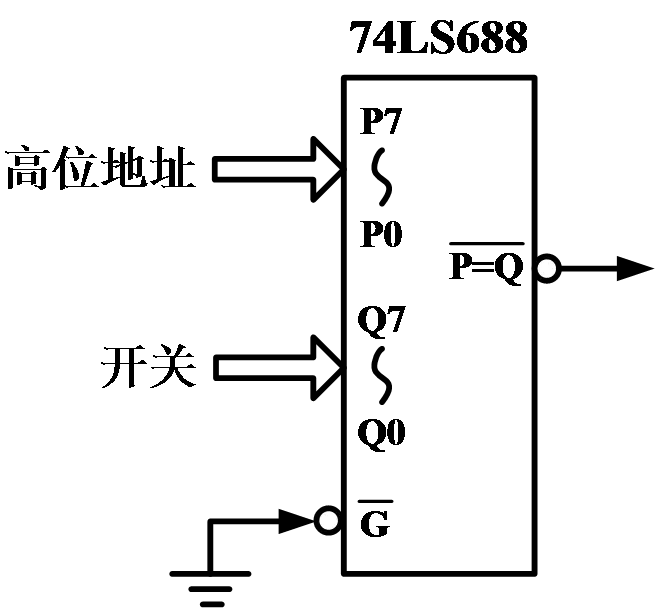

- 防止总线竞争的原则:只有当CPU读本电路板内的内存地址/接口地址时,才允许双向驱动器指向系统总线的三态门是导通的

- 步骤

- 分析板内内存地址,找出地址特征

- 设置译码电路,用来控制双向数据总线驱动器,使之满足防止总线竞争的原则

- 译码方式

- 基本门电路

- 译码器(74LS138)

- 译码ROM

- 比较器(74LS688)

- PLA CPLD FPGA

第三讲 总线的工程设计问题

- 设计总线要考虑

- 不发生总线竞争

- 总线负载

- 总线交叉串扰

- 总线延时

- 总线信号的反射

- 总线交叉串扰

- 产生原因

- 总线间的寄生电容

- 总线本身可看做一个小电感

- 解决:减少总线间的寄生电容

- 减少总线长度

- 增加总线间距离

- 降低总线上的负载

- 两条信号线间加一条地线

- 减少总线的平行走向

- 总线优化器DS36662

- 采用双绞线

- 产生原因

- 总线延时

- 解决方法

- 减少总线长度

- 选用延时小、输入输出电容小、驱动能力强的元器件

- 解决方法

- 总线信号的反射

- 产生原因:

- 信号沿总线传播到达总线终端时,若总线终端负载阻抗与总线特性阻抗不匹配,信号的一部分会被反射

- 反射回来的信号到达信号源时,若源的内部阻抗与总线的特性阻抗不匹配,又会有一部分被反射回去

- 此过程有时需要多次才能在负载上建立所需的波形

- 危害

- 反射使波形变坏、延时增加

- 克服方法

- 降低传输信号的频率

- 尽量使 信号源内阻、总线的特性阻抗、负载阻抗 相匹配

- 总线匹配

- 末端匹配

- 源端匹配

- 总线匹配

- 限制总线长度

- 产生原因:

第五章 存储技术

第一讲 概述

半导体存储器的基本概念

- RAM: SRAM [异步 SRAM, 同步 SRAM], DRAM

- ROM

- 可一次编程 ROM: PROM(Programmable ROM);

- 可擦写的 PROM: [EPROM(Erasable Programmable ROM),

E2PROM/EEPROM(Electrically Erasable Programmable ROM)[传统 E2PROM, FLASH]]

- 三级存储结构: 高速缓冲存储器、主存储器、辅助存储器

第二讲 常用存储器芯片及接口设计

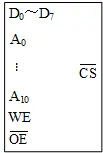

SRAM 及接口设计

- 异步 SRAM: 访存独立于时钟,控制信号不需要时钟同步

- 同步 SRAM: 访存依赖于时钟,控制信号需要时钟同步

第三讲 Intel16/32/64 位微机系统的主存设计

- 8088 系统存储器: 8 位数据总线,单体存储器

- 8086/186/286 系统: 16 位数据总线,双体存储器

存储器结构

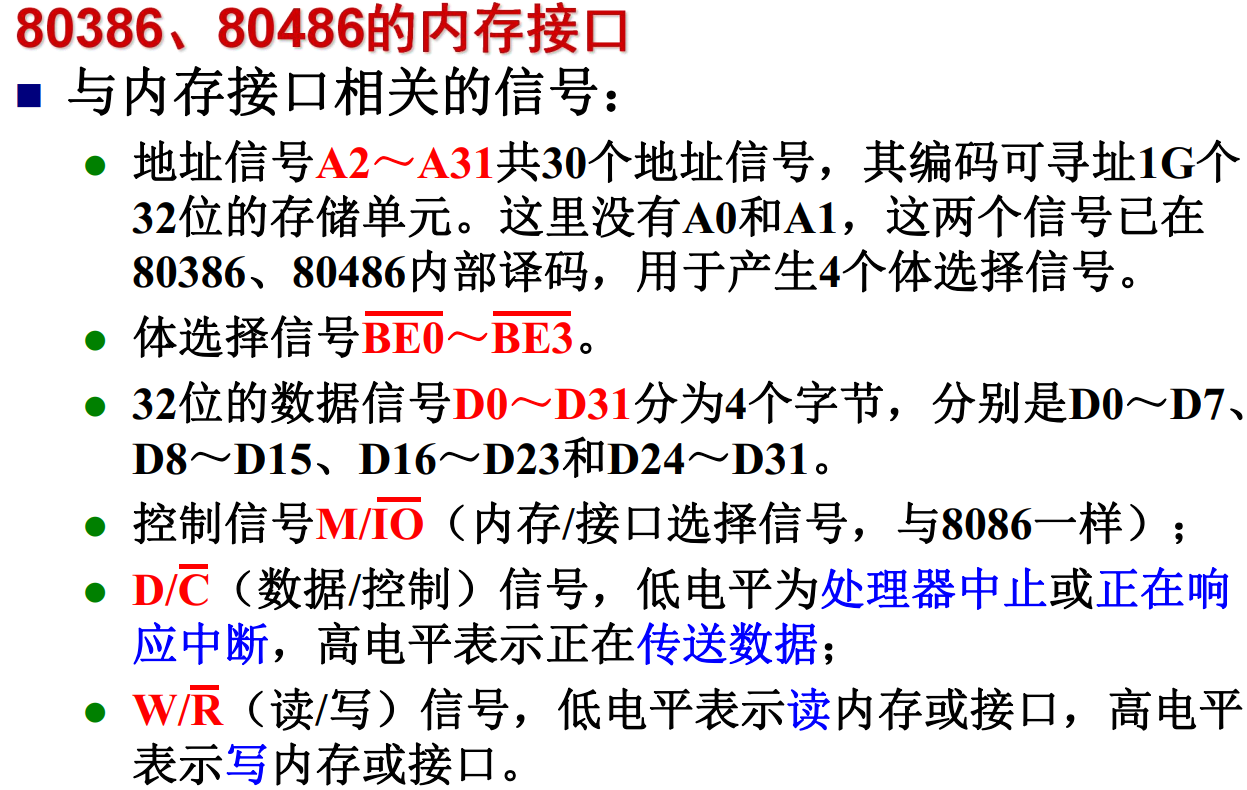

- 80386/80486 系统: 32 位数据总线,四体存储器

- Intel 16位微机系统的主存设计

- 存储器的字、位扩展

- 芯片数量计算

- 存储容量 = (尾地址 - 首地址 + 1)× 位宽

- 芯片数量 = 存储容量/芯片容量

- Intel 32位微机系统的主存设计

接口信号

| M/¯IO | D/¯C | W/¯R | 总线周期 |

|---|---|---|---|

| 0 | 0 | 0 | 中断响应 |

| 0 | 0 | 1 | 停机 |

| 0 | 1 | 0 | I/O读 |

| 0 | 1 | 1 | I/O写 |

| 1 | 0 | 0 | 取指令操作码 |

| 1 | 0 | 1 | 保留 |

| 1 | 1 | 0 | 存储器读 |

| 1 | 1 | 1 | 存储器写 |

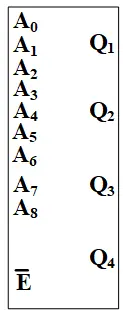

- Intel 64位微机系统的主存设计

- 体选择信号: ¯BE0 ~ ¯BE7

- 内存由 8 个体构成,每个体对应一个体选择信号

第四讲 只读存储器 (ROM) 及接口设计

外存平均访问时间 ms 级; 内存平均访问时间 ns 级

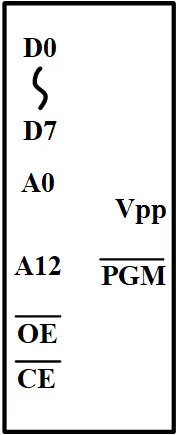

EPROM

- 需要进行擦除

EEPROM

- 可单字节随机读写 (不需擦除,直接改写数据)

- 存储密度小,单位成本高

第六章 输入/输出技术

第一讲 I/O概述

主机和外设

I/O 方式

- 程序控制方式

- 无条件传送方式

- 查询方式 不要求CPU效率 外设慢速

- 中断方式 要求CPU效率 外设中慢速

- DMA 外设高速

从无条件传送方式到DMA,控制越来越复杂,效率越来越高

I/O 接口

作用

- 信息传递(利用端口——接口里的寄存器)

- 注意区分“接口”“端口”

- 数据格式转换

- CPU与外设速度匹配

- 负载匹配、时序匹配

- 总线隔离

- 提供中断、DMA功能

- 信息传递(利用端口——接口里的寄存器)

信息传递

编址方式

- 统一编制

- 独立编制(有IN OUT)

I/O 端口地址译码

- 全地址译码

- 部分地址译码

基本的并行输入/输出接口

- 输入:三态门(防止总线冲突)

- 输出:锁存器(CPU和外设速度匹配)

第二讲 程序查询 I/O 方式

无条件传送方式(查询方式的特例)

- 外设时刻处于就绪状态

- 硬件:数据端口,软件:输入输出指令

查询方式

外设准备就绪之后才能与微机系统进行信息交换

硬件:数据端口、状态端口,软件:不断查询 ;硬件简单,软件开销大

时序

多外设的查询控制

一定要服务优先级高的——用于优先级差别很大的

服务完高优先级的再从头查询——用于优先级有一定差距的

机会均等——用于优先级差别很小的

第三讲 中断方式

中断概述

- 中断源

- 内部:内中断(软件中断)

- 外部:外中断(硬件中断)

- NMI(不可屏蔽)

- INTR(可屏蔽)

- 中断过程

- 中断源发出中断请求

- 满足中断条件,进行中断响应

- 断点保护(硬件完成)

- PSW压栈,关中断,CS压栈,IP压栈

- 中断判优

- 硬件判优

- 软件判优

- 中断源识别

- 软件查询

- 中断矢量法

- 获得中断服务子程序首地址

- 固定入口法

- 中断向量法

- 断点保护(硬件完成)

- 中断处理——中断服务子程序

- FAR类型,用IRET返回

- 保护现场 → 开中断STI → 中断处理 → 关中断CLI → 恢复现场 → 中断返回IRET

- RISC寄存器分页,中断服务程序无需PUSH POP

- 中断返回 IRET

- IRET指令使CPU把堆栈内保存的断电信息弹出到IP、CS、FLAG中

- 中断优先级嵌套

- 优先级原则

- 速度快>速度慢

- 输入设备>输出设备

- 解决办法

- 软件查询

- 硬件链式优先级排队电路

- 硬件优先级编码比较电路

- 利用可编中断控制器PIC

- 实现中需注意

- 中断处理程序:STI开中断指令

- 堆栈足够大

- 正确使用堆栈(关中断之后恢复现场)

- 优先级原则

Intel 16位中断系统

8086/8088中断系统

- 中断源类型

- 中断向量表IVT

- 存放中断服务程序的入口地址

- 00000H ~ 003FFH,1KB = 4B/入口 × 256个入口

- 中断向量在IVT中的存放地址 = 4 × 中断类型号n

- 4n : IP

- 4n+2 : CS

- 中断的响应过程

- 注意,外部中断INTA有两次

- 优先级从高到低:内部中断、NMI 、INTR、单步中断

可编程中断控制器(PIC)8259

内部结构

- IRR 请求(=1表示有请求)

- ISR 服务(=1表示正被服务)

- IMR 屏蔽(=1表示被屏蔽)

- 中断优先权判别电路

引脚

工作方式

级联

- 单片8259A可支持8个中断源,多片级联最多支持64个中断源,n片可支持7n+1个中断源(n≤9)

- ¯SP / ¯EN :低-从片,高-主片

- 从片中断结束,中断服务程序需发送两个EOI命令

编程使用

内部寄存器的寻址方法

命令字

中断方式实现方法

- 特点

- 高速外设,纯硬件控制,外设直接与存储器进行数据交换,无需CPU,传输速率高

- 内存/外设的地址和读写控制均由DMACA提供

- 时序

- AEN=0 : CPU

- AEN=1 : DMA

- 工作过程

- 外设准备好,向DMA发出DRQ

- DMA收到请求,向CPU发出HOLD

- CPU完成当前总线周期且非总线封锁,响应HOLD信号

- 将数据总线、地址总线、控制信号线置高阻态,放弃总线控制权

- 向DMA发出HLDA

- DMA收到HLDA,开始控制总线,向外设发出DACK

- 外设与内存 或 内存与内存 直接数据传送

- DMA自动修改地址和字节计数器,传完后,撤HOLD

- CPU撤HLDA,下一时钟周期控制总线

DMA控制器8237(DMAC)

- 特点

- 4个独立DMA通道,级联扩展为最多16个

- 引脚及功能

- 工作时序

Si:空闲状态

S0请求状态

S1 ~ S4传送状态 - 工作方式

- 空闲周期

- 工作周期

- 传输方式

- 单字节传送(传完一个字节后,DREQ无效,总线控制权还给CPU)

- 数据块传送 (传完块数据后才释放总线,期间无论DREQ是否有效都传送)

- 请求传送(猝发传送)(只要DREQ有效或I/O接口的数据缓冲可用,DMA一直传送数据)

- 连接方式

- 级联方式

- 在级联方式下,当第二层8237的请求得到响应时,第一层8237仅向微处理器发出HRQ信号、对第二层的HRQ作出响应DACK而不能输出地址及控制信号,第二层的8237才是真正的主控制器

- 传输方式

- 传送类型:存储器 → 接口,接口 → 存储器,存储器 → 存储器

- 优先级

- 固定优先级

- 循环优先级

- 传输速率

- 正常时序(1个DMA总线周期需4个时钟周期)

- 压缩时序(1个DMA总线周期需2个时钟周期)

- 内部寄存器

第七章 常用接口器件

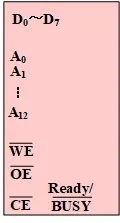

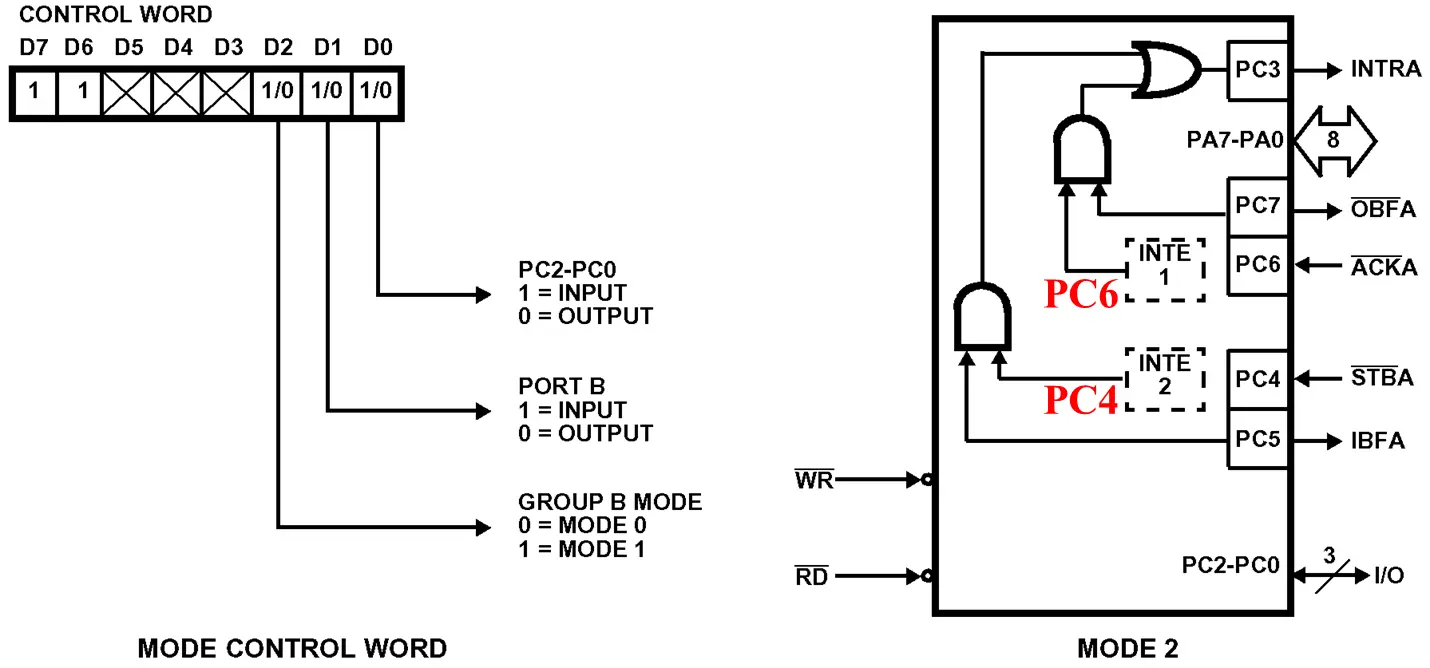

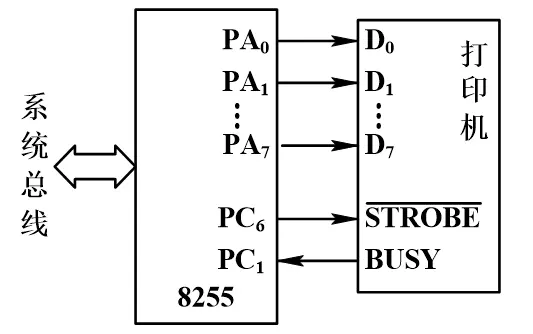

第一讲 8255: 8位通用可编程并行接口

计算机与外设之间通过接口传送数据

- 无条件输入(三态门: 74LS244)

- 无条件输出(锁存器: 74LS273)

- 中断方式,单向输入/输出

- 中断方式,双向传输(I/O)

端口地址信号

| A1 | A0 | 选择 |

|---|---|---|

| 0 | 0 | A口(PA0∼PA7) |

| 0 | 1 | B口(PB0∼PB7) |

| 1 | 0 | C口(PC0∼PC7) |

| 1 | 1 | 控制寄存器 |

A口、B口的输入和输出具有锁存能力,C口的输出有锁存能力,输入没有锁存能力

| A组 | B组 |

|---|---|

| PA0∼PA7,PC4∼PC7 | PB0∼PB7,PC0∼PC3 |

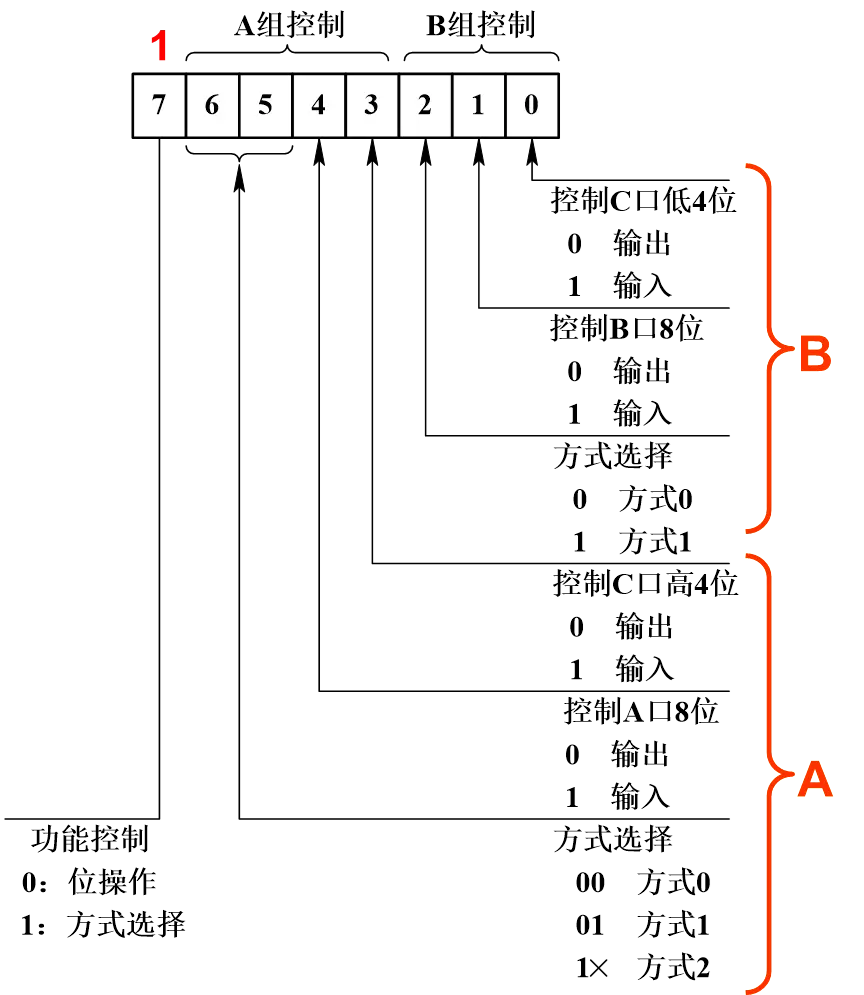

控制字

8255的方式选择控制字格式

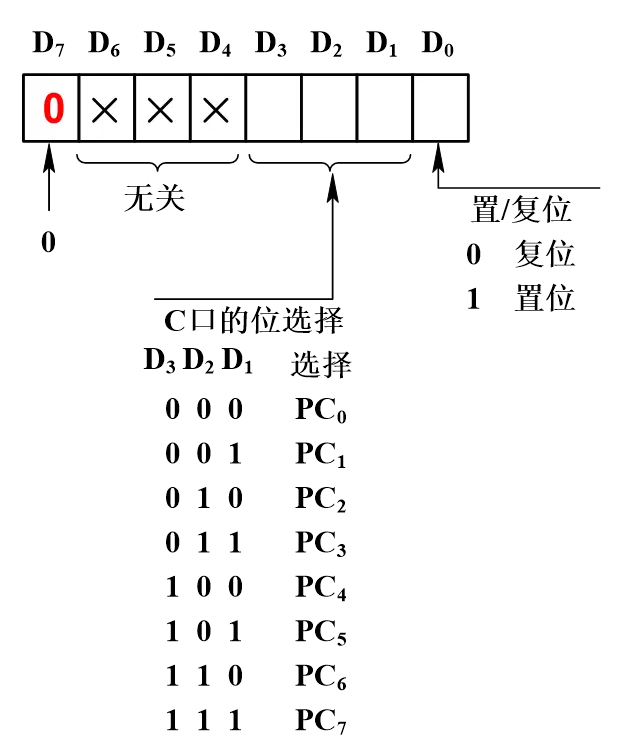

8255的按位操作控制字格式

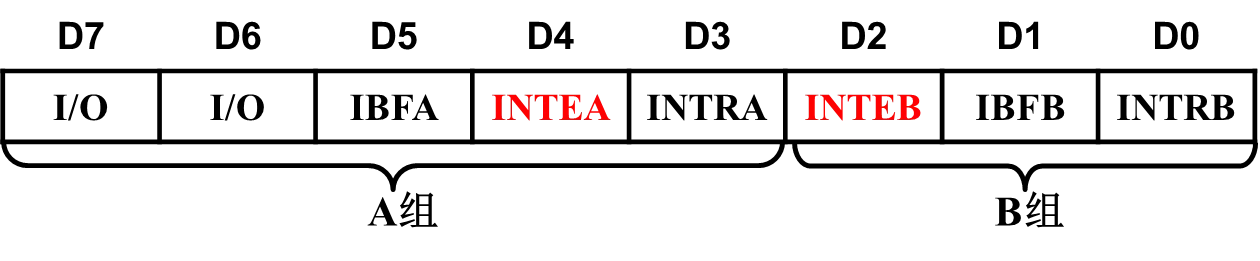

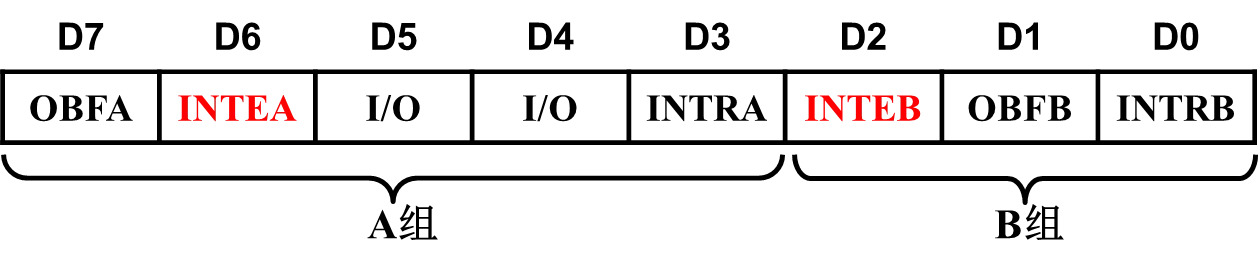

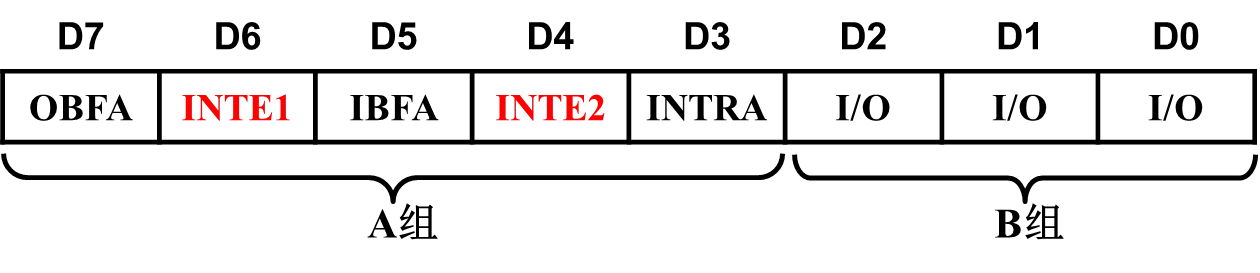

状态字

当8255的A口、B口工作在方式1或A口工作在方式2时,通过读C口的状态,可以检测A口和B口的状态

A、B口均为方式1输入时的状态字

A、B口均为方式1输出时的状态字

A口在方式2工作时的状态字

工作方式

- 工作方式 0(基本输入/输出方式)

A口(PA0∼PA7)、B口(PB0∼PB7)、C口低四位(PC0∼PC3)、C口高四位(PC4∼PC7)独立定义,均可做为输入或输出接口 - 工作方式 1(选通输入/输出方式)

芯片结构连接图

初始化程序

1 | INIT_8255: |

1 | INIT_8255: |

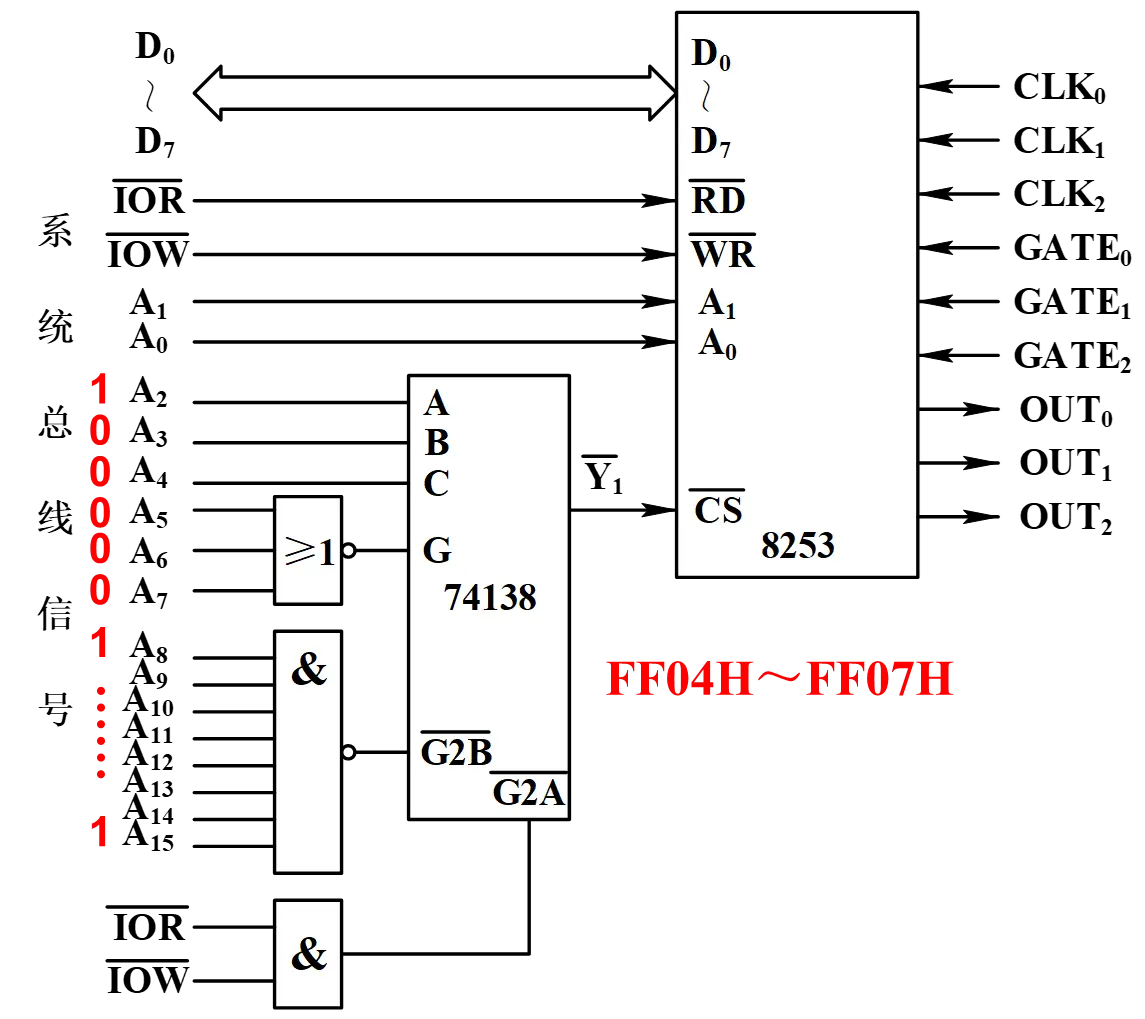

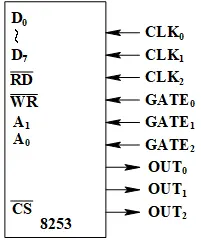

第二讲 8253: 可编程定时器

端口地址信号

| A1 | A0 | 选择 |

|---|---|---|

| 0 | 0 | 计数器0 |

| 0 | 1 | 计数器1 |

| 1 | 0 | 计数器2 |

| 1 | 1 | 控制寄存器 |

芯片结构

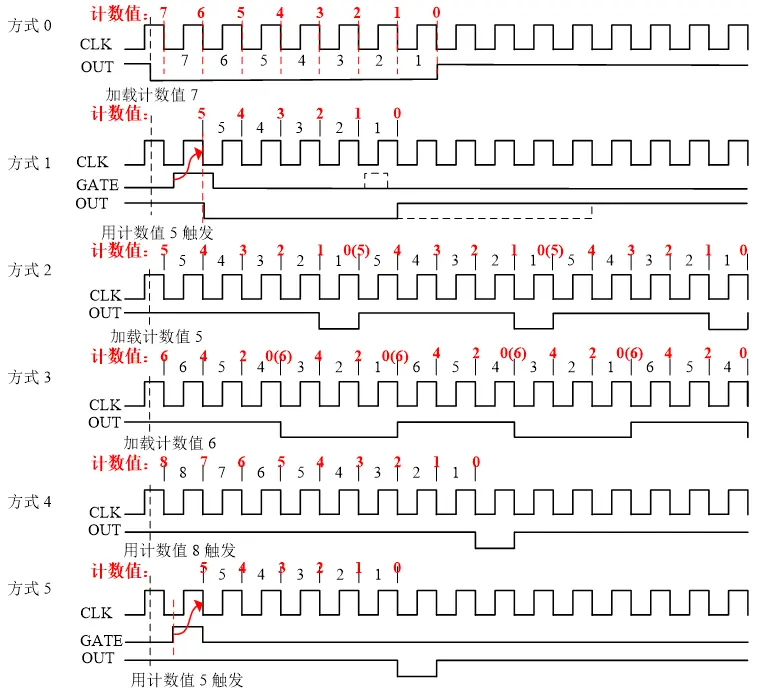

计数方式

- 方式0:计数结束产生中断

- Condition: GATE 高电平,允许计数

- OUT: 输出低电平

- First CLK: 计数初值 N -> 初值寄存器

- N CLKs: 减一计数

- N+1 CLKs: 事件计数

- 方式1:可编程单稳

- Condition: GATE 上升沿触发计数

- OUT: 输出低电平

- N CLKs: 利用 GATE 编程计数

- 方式2:频率发生器

- Condition: GATE 高电平,允许计数

- OUT: 周期输出负脉冲

- N CLKs: 减到1时送出负脉冲

- 方式3:方波发生器

- Condition: GATE 高电平,对称方波

- OUT: 前 N/2 | (N+1)/2 CLKs 高电平,后 N/2 | (N-1)/2 CLKs 低电平

- 方式4:软件触发选通

- Condition: GATE 高电平,允许计数

- OUT: 计数结束输出负脉冲

- N CLKs: 技术结束下一个 CLK, 送出负脉冲

- 方式5:硬件触发选通

- Condition: GATE 上升沿触发计数

- OUT: 计数结束输出负脉冲

- N CLKs: 技术结束下一个 CLK, 送出负脉冲

- Summary

- 所有 GATE 上升沿触发计数均在下一个 CLK 启动计数

- 0为计数最大值,1为计数最小值,计数为减一计数器

- 从初值寄存器装入新的计数值,除了可编程单稳,频率发生器都需要重新开始计数

- 所有 GATE 上升沿触发计数(可编程单稳,频率发生器)在新的上升沿到来时,均会重新开始计数

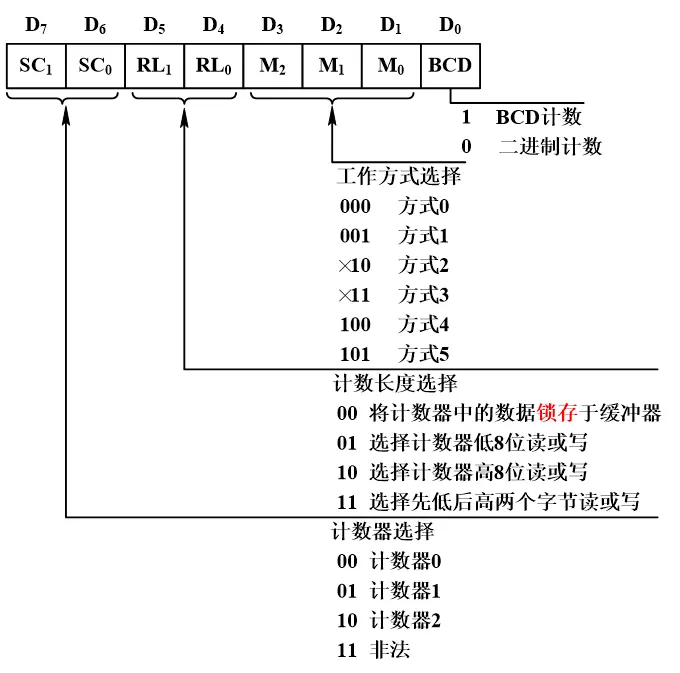

控制字

芯片结构连接图

初始化程序及其应用

1 | MOV AL, 36H ; 控制字,计数器0,双字节,方式3,二进制计数 |

- 计数模式1:GATE周期信号频率: F1Hz, CLK输入频率: F2Hz,GATE上升沿刷新计数的最大计数值为:

N=F2F1

题型分析

第二章 8086/8088 CPU

- 8086/8088 最小/最大模式下系统总线形成

第三章 8086汇编语言程序设计

- 常用汇编指令

- 基本汇编程序编写

- 基本表达式计算

- 数据段中数组数据进行排序

第四章 总线与驱动控制

- 常用数据总线特点(ISA, PCI, USB)

- 总线驱动控制电路设计与分析

- 单向驱动器: 74LS224

- 双向驱动器: 74LS245

- 数据锁存器: 74LS373

- 总线驱动与控制参数计算

第五章 存储器设计

- SRAM, DRAM, EPROM, EEPROM 特点

- 数字比较器、PROM 作为译码电路的实现机制

- 基于 SRAM 芯片的8086/88系统主存电路设计与分析

- 位扩展+字扩展设计方法(8086系统16位存储设计)

- 8086系统8位读写以及16位读写

- 总线驱动设计: 单向驱动与双向驱动

- 基于 EEPROM 芯片的 IO 接口设计(Busy的处理)

- 存储器设计中总线驱动器件使能端设计

第六章 输入/输出技术

- 中断处理响应过程

- 8259工作方式(状态字)

- 级联: 特殊全嵌套与一般嵌套

- 中断结束: 自动EOI, 特殊/指定EOI, 一般/非指定EOI

- 优先级: 固定优先级, 自动循环优先级, 指定循环优先级

必要细节处理

…

Extend Points

…